# **OPEN** Compute Project

Caliptra: A Datacenter System on a Chip (SOC) Root of Trust (RoT)

**Revision 1.0**

Version 0.5

#### **CONTRIBUTORS:**

Bryan Kelly (Microsoft)

Andrés Lagar-Cavilla (Google)

Jeff Andersen (Google)

Prabhu Jayana (AMD)

Piotr Kwidzinski (AMD)

Rob Strong (AMD)

John Traver (AMD)

Louis Ferraro (AMD)

Ishwar Agarwal (Microsoft)

Anjana Parthasarathy (Microsoft)

Bharat Pillilli (Microsoft)

Vishal Soni (Microsoft)

Marius Schilder (Google)

Sudhir Mathane (AMD)

Nathan Nadarajah (AMD)

Kor Nielsen (Google)

#### **Revision Table**

| Date           | Revision # | Author                                                                                                                                 | Description                                                                                                                                                                                                |

|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2022  | 0.2        | Prabhu Jayana (AMD)<br>Bryan Kelly (Microsoft)<br>Piotr Kwidzinski (AMD)<br>Andrés Lagar-Cavilla<br>(Google)<br>Jeff Andersen (Google) | Initial proposal draft                                                                                                                                                                                     |

| March 2022     | 0.4        | Rob Strong (AMD)<br>Piotr Kwindzinski (AMD)<br>Prabhu Jayana (AMD)                                                                     | <ul> <li>Migrated to OCP<br/>template</li> <li>edits to clarify<br/>language use and<br/>added sections<br/>related LifeCycle<br/>support, fuse, crypto<br/>requirements, Kat<br/>support, etc.</li> </ul> |

| April 12, 2022 | 0.5        | Rob Strong (AMD)                                                                                                                       | Various edits and<br>formatting<br>modifications to get<br>to v.5                                                                                                                                          |

| June 2022      | 0.51       | Rob Strong (AMD)                                                                                                                       | Updated the FW<br>Signing/Verification<br>Algorithms section -<br>added references to<br>OCP Secure Boot<br>specification.                                                                                 |

|             |      |                                                | Updated Physical<br>Attack<br>Countermeasures -<br>updated the section<br>to reference NiST<br>paper ([14]) that<br>discusses SCA as<br>well as their<br>countermeasures. |

|-------------|------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2022   | 0.52 | Nathan Nadarajah (AMD)<br>Sudhir Mathane (AMD) | Added Threat Model<br>section and initial<br>content<br>(work-in-progress)                                                                                                |

| July 2022   | 0.53 | Louis Ferraro (AMD)                            | Added Device<br>Resilience chapter<br>and updated related<br>text.                                                                                                        |

| August 2022 | 0.54 | Piotr Kwidzinski (AMD)                         | Updated with OCP<br>template and<br>feedback. Added<br>License and<br>Appendix sections.                                                                                  |

# **Table of Contents**

License Open Web Foundation (OWF) CLA **1.2 Acknowledgements** Scope **Overview** Acronyms and Abbreviations **Requirements Terminology References** Theory of Operation Silicon RoT Goals **Use Cases** Supply Chain Security **DICE-as-a-Service** Industry Standards and Association / Consortium Specifications NIST SP800-193 Platform Firmware Resiliency Trusted Computing Group (TCG) DICE Attestation Threat Model **Attacker Profiles** Types of Attacks **Physical Attacks** Logical Attacks **Trust Boundaries** Caliptra Assets & Threats High Level Architecture **Caliptra Profiles** Active Profile **Passive Profile** Identity <u>UDS</u> IDevID key LDevID key FMC alias key Security state **Owner endorsement** Provisioning IDevID during manufacturing

| Certificate Format                                               |

|------------------------------------------------------------------|

| Caliptra Security States                                         |

| Service Surface                                                  |

| Device Resilience                                                |

| Secure Boot Flow                                                 |

| Caliptra RTM hitless update                                      |

| Anti-rollback Support                                            |

| Informative comment: Example                                     |

| Physical Attack Countermeasures                                  |

| Compliance and Certification Requirements                        |

| Known Answer Test (KAT) Support                                  |

| FW Signing/Verification Algorithms [updated]                     |

| Post-Quantum Cryptography (PQC) Requirements                     |

| Key Rotation                                                     |

| HW Section                                                       |

| HW Block Diagram                                                 |

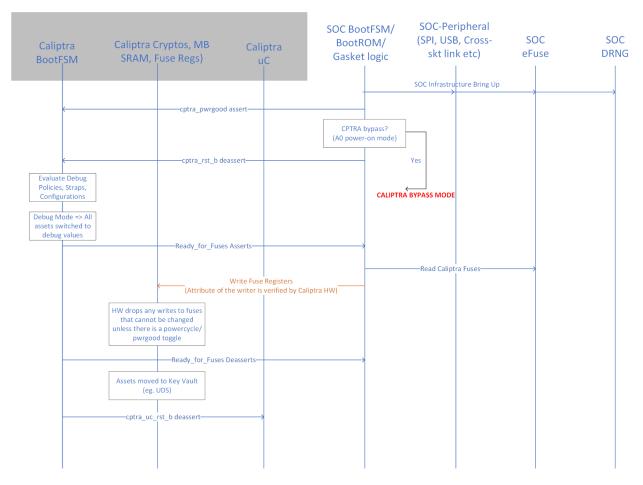

| Caliptra IP HW Boot Flow                                         |

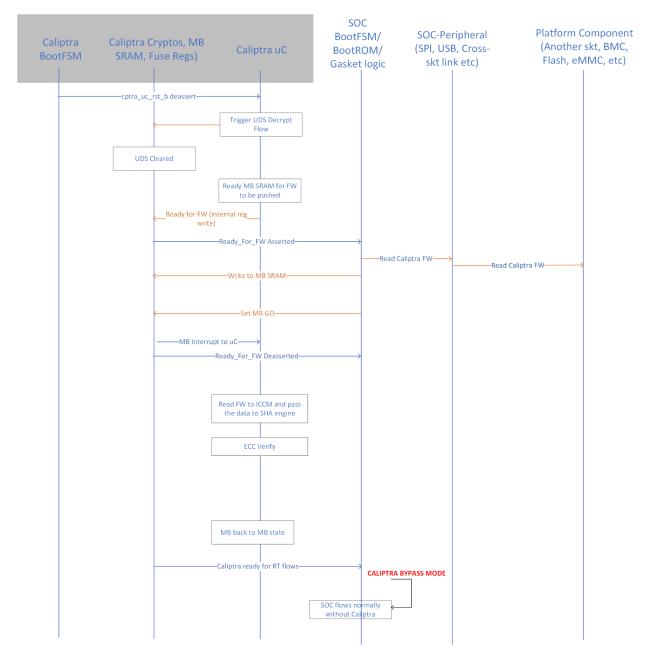

| Caliptra FW Push Flow (Passive mode)                             |

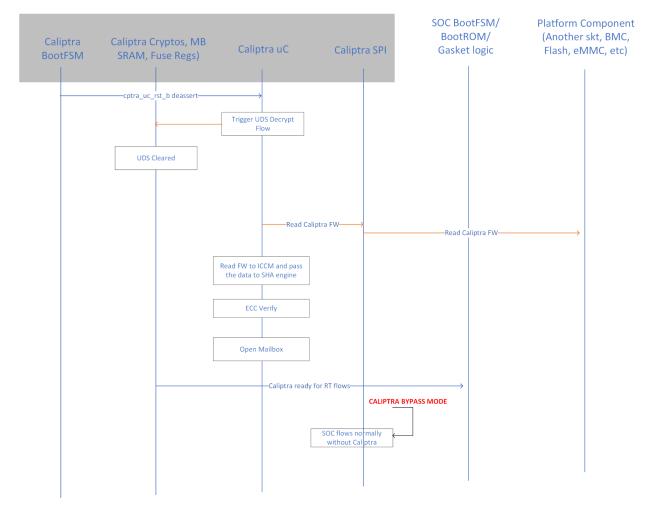

| Caliptra IP FW Load Flow (Active Mode)                           |

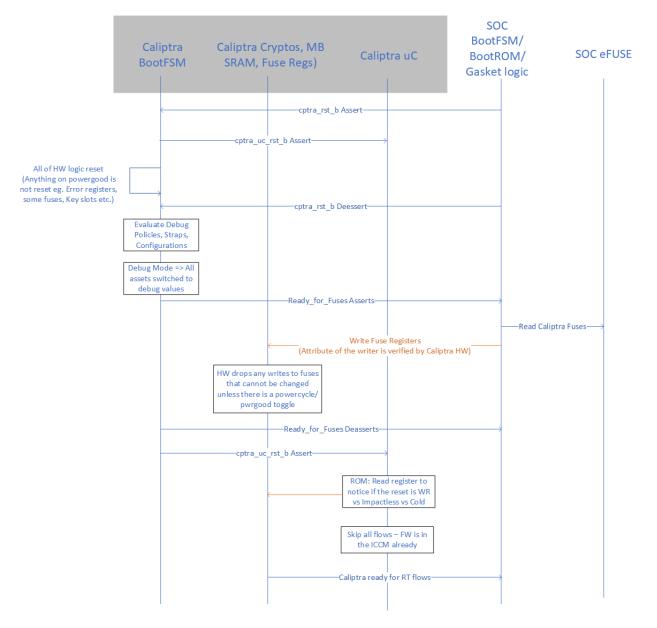

| <u>CPU Warm Reset or PCIe Hot Reset Flow → Caliptra IP reset</u> |

| <u>Mailbox</u>                                                   |

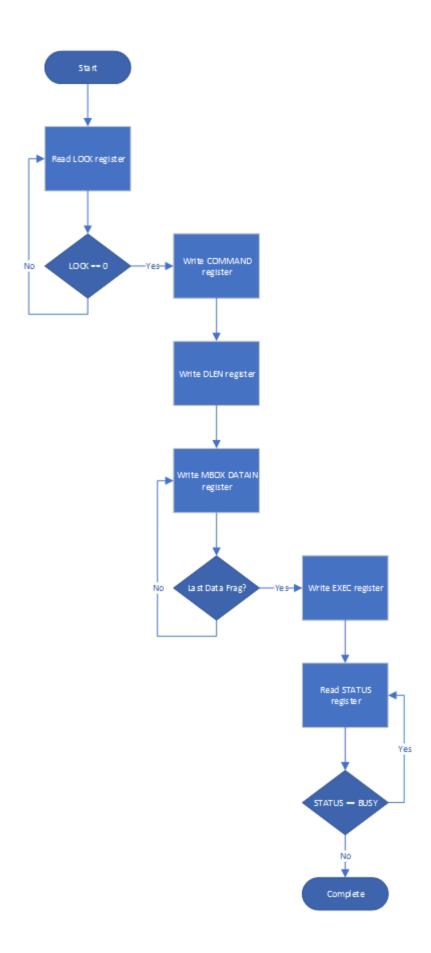

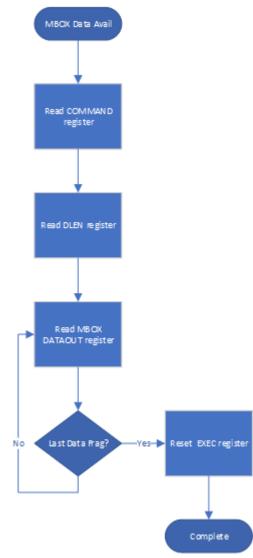

| Sender Protocol                                                  |

| Receiver Protocol                                                |

| <u>User Attributes</u>                                           |

|                                                                  |

Architectural Registers

Fuse Requirements

Fuse Programming

Fuse Zeroing

Error Reporting and Handling [0.8 release]

<u>Appendix A - Checklist for IC approval of this Specification (to be completed by contributor(s) of this Spec)</u>

<u>Appendix B-\_\_\_\_

supplier name> - OCP Supplier Information and Hardware Product</u>

<u>Recognition Checklist</u>

Appendix C - Contribution Process FAQs

# License

## **Open Web Foundation (OWF) CLA**

Contributions to this Specification are made under the terms and conditions set forth in Open Web Foundation Modified Contributor License Agreement ("OWF CLA 1.0") ("Contribution License") by:

#### AMD Google Microsoft

Usage of this Specification is governed by the terms and conditions set forth in **Open Web** Foundation Modified Final Specification Agreement ("OWFa 1.0") ("Specification License").

You can review the applicable OWFa1.0 Specification License(s) referenced above by the contributors to this Specification on the OCP website at <a href="http://www.opencompute.org/participate/legal-documents/">http://www.opencompute.org/participate/legal-documents/</a>. For actual executed copies of either agreement, please contact OCP directly.

#### Notes:

1) The above license does not apply to the Appendix or Appendices. The information in the Appendix or Appendices is for reference only and non-normative in nature.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION. INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING

NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

#### Acknowledgements

The Contributors of this Specification would like to acknowledge the following companies for their feedback:

# **Compliance with OCP Tenets**

Please describe how this Specification complies to the following OCP tenets. Compliance is required for at least three of the four tenets. The ideals behind open sourcing stipulate that everyone benefits when we share and work together. Any open source project is designed to promote sharing of design elements with peers and to help them understand and adopt those contributions. There is no purpose in sharing if all parties aren't aligned with that philosophy. The IC will look beyond the contribution for evidence that the contributor is aligned with this philosophy. The contributor actions, past and present, are evidence of alignment and conviction to all the tenets.

#### Openness

The Caliptra source for RTL and firmware will be licensed using the Apache 2.0 license. The specific mechanics and hosting of the code are work in progress due to CHIPS alliance timelines. Future versions of this spec will point to the relevant resources.

#### Efficiency

Caliptra is used during the boot sequence and upgrade cycles, so it cannot yield a measurable impact on system efficiency.

#### Impact

Caliptra brings consistency and transparency to a foundational area of security and confidential compute. Open source in-package RoTs have not been attempted before in the industry. It is challenging to align partners, and it is challenging to align a common core of functionality everyone agrees upon in this space. Caliptra breaches multiple traditional blockers and creates new ground for the industry and for open ecosystems.

#### Scale

Caliptra is a committed intercept for Google and Microsoft first party Cloud silicon. It is also a committed intercept for AMD server silicon products. This scale covers both a significant portion of the Cloud market as well as one of the two key CPU vendors in hyperscale and enterprise.

# Scope

This document defines technical specifications for a Caliptra RTM<sup>1</sup> used in Open Compute Project. This document, along with the [baseline specification] shall comprise product's technical specification.

# Overview

This document provides definitions and requirements for a Caliptra RTM. The document then relates these definitions to existing technologies, enabling third device and platform vendors to better understand those technologies in trusted computing terms.

# Acronyms and Abbreviations

For the purposes of this document, the following abbreviations apply:

## Abbreviation

Description

<sup>&</sup>lt;sup>1</sup> Caliptra. Spanish for "root cap" and describes the deepest part of the root

| BMC    | Baseboard Management Controller                |

|--------|------------------------------------------------|

| CA     | Certificate Authority                          |

| CDI    | Composite Device Identifier                    |

| CPU    | Central Processing Unit                        |

| CRL    | Certificate Revocation List                    |

| CSR    | Certificate Signing Request                    |

| CSP    | Critical Security Parameter                    |

| DICE   | Device Identifier Composition Engine           |

| DME    | Device Manufacturer Endorsement                |

| DRBG   | Deterministic Random Bit Generator             |

| ECDSA  | Elliptic Curve Digital Signature Algorithm     |

| FMC    | FW First Mutable Code                          |

| GPU    | Graphics Processing Unit                       |

| IDevid | Initial Device Identifier                      |

| iRoT   | Internal RoT                                   |

| КАТ    | Known Answer Test                              |

| LDevid | Locally Significant Device Identifier          |

| МСТР   | Management Component Transport Protocol        |

| NIC    | Network Interface Card                         |

| NIST   | National Institute of Standards and technology |

| OCP    | Open Compute Project                           |

| ОТР    | One-time programmable                          |

| РКІ    | Public Key infrastructure                      |

| PUF    | Physically unclonable function                 |

|        |                                                |

| RoT  | Root of Trust                       |

|------|-------------------------------------|

| RTI  | RoT for Identity                    |

| RTM  | RoT for Measurement                 |

| RTR  | RoT for Reporting                   |

| SoC  | System on Chip                      |

| SPDM | Security Protocol and Data Model    |

| SSD  | Solid State Drive                   |

| тсв  | Trusted Computing Base              |

| ТСІ  | TCB Component Identifier            |

| TCG  | Trusted Computing Group             |

| TEE  | Trusted Execution Environment       |

| TRNG | True Random Number Generator        |

| UECC | Uncorrectable Error Correction Code |

# **Requirements Terminology**

The key words "MUST", "MUST NOT", "REQUIRED", "SHALL", "SHALL NOT", "SHOULD", "SHOULD NOT", "RECOMMENDED", "NOT RECOMMENDED", "MAY", and "OPTIONAL" in this document are to be interpreted as described in [BCP 14] [RFC2119] [RFC8174] when, and only when, they appear in all capitals, as shown here.

# References

[1] NIST Special Publication 800-193 Platform Firmware Resiliency Guidelines

[2] IEEE Standard for Local and Metropolitan Area Networks Secure Device Identity

[3] DMTF Security Protocol and Data Model (SPDM) Specification (DSP0274)

[4] OCP Security WG: Ownership Transfer

[5] Global Platform Technology Root of Trust Definitions and Requirements Version 1.1 Public Release June 2018

[6] TCG DICE Layering Architecture Version 1.0 Revision 0.19 July 23, 2020

[7] NIST Special Publication 800-56A Revision 3 Recommendation for Pair-Wise Key-Establishment Schemes Using Discrete Logarithm Cryptography

[8] NIST Special Publication 800-108 Recommendation for Key Derivation Using Pseudorandom Functions

[9] NIST Special Publication 800-208 Recommendation for Stateful Hash-Based Signature Schemes

[10] Ownership and Control of Firmware in Open Compute Project Devices (Open Compute Project, Security WG)

[11] Open Compute Project Secure Boot Specification

[12] TCG DICE Attestation Architecture Version 1.00 Revision 0.23 March 1, 2021

[13] TCG Hardware Requirements for a Device Identifier Composition Engine Family "2.0" Level 00 Revision 78 March 22, 2018

[14] <u>Side-Channel Attacks: Ten Years After Its Publication and the Impacts on Cryptographic</u> <u>Module Security Testing</u>

[15] Attestation V1.0 White Paper

# Theory of Operation

Establishing a core root of trust along with a chain of trust that attests to the integrity of configuration and mutable code is fundamental to the overall security posture of silicon devices.

Traditional RoT architectures have offered a multitude of intrinsic security services and hosted security applications on a trusted execution environment (TEE) that consist of (but not limited to) hardware capabilities (cryptographic and microprocessor), ROM, Firmware & API infrastructure. These solutions have been instantiated in discrete or integrated forms in various platform & component architectures.

Some of these solutions are either proprietary or aligned to specific parts of an industry standards/consortium/association specifications (e.g.,National Institutes of Standards and technology (NIST), Open Compute Project (OCP), Trusted Computing Group (TCG), Distributed Management Task Force (DMTF), Institute of Electrical and Electronics Engineers (IEEE), etc.) and may be certified to various conformance standards (e.g., NIST cryptographic algorithm Validation program (CAVP), etc.).

Establishing a consistent root of trust on very different hardware configurations while maintaining configuration and deployment flexibility is challenging. There is no uniform configuration across Cloud Service Providers. Example: A system with host processors, has very different firmware security measures when compared to systems without head-nodes or host processors.

The OCP Security WG specifications are making progress towards establishing the platform and peripheral security architecture <u>recommendations</u> necessary to attain the desired consistency in platform security orchestration.

The objective of this specification is to define core RoT capabilities that must be implemented in the SoC or ASIC of any device in a cloud platform. The collection of these RoT capabilities is referred to as the *Silicon RoT Services (Silicon RoT)*.

# Silicon RoT Goals

The scope of a Caliptra Silicon RoT is deliberately minimalistic in nature to drive agility of specification definition, to maximize applicability, and to drive industry alignment, consistency and faster adoption of foundational device security primitives. A well and narrowly defined specification maximizes architectural composability, reusability across CSPs, products and vendors, and feasibility of open sourcing.

Enhancements, advanced use cases & applications are outside the scope of this specification and may be developed in the form of a roadmap for the Silicon RoT and community engagement.

Caliptra defines a design standard for a Silicon internal RoT baseline. The standard satisfies a Root of Trust for Measurement (RTM) role. The open-source implementation of Caliptra drives transparency into the RTM and measurement mechanism that anchors hardware attestation. The Caliptra Silicon RoT must boot the SoC, measure the mutable code it loads, and measure and control mutation of non-volatile configuration bits in the SoC. The Caliptra Silicon RoT reports these measurements with signed attestations rooted in unique per-asset cryptographic entropy. As such, the Caliptra Silicon RoT serves as a Root of Trust for Identity for the SoC.

No other capabilities are part of this specification, to satisfy the criteria for success outlined above, and to decouple platform integrity capabilities that can be enforced and evolve independently via other platform devices or services – such as Update, Protection and Recovery.

Within this scope, the goals for a Caliptra 1.0 specification include:

- Definition and design of the standard silicon internal RoT baseline:

- Reference functional specification:

- Scope including RTM and RTI capabilities

- Control over SoC non-volatile state, including per asset entropy

- Reference APIs:

- Attestation APIs

- Internal SoC services

- Reference implementation

- Open Source Reference ( including RTL and firmware reference code):

- For implementation consistency, leverage open source dynamics to avoid pitfalls and common mistakes

- For accelerated adoption (e.g., so that future products can leverage existing designs and avoid having to start the design process from scratch)

- For greater transparency, to avoid fragmentation in the implementation space

- Firmware and RTL logical design are open, managed by consortium.

- Consistency across the industry in the internal RoT (iRoT) architecture and

implementation

- DICE Identity, Measurement & Recovery

- The silicon iRoT scope includes all datacenter-focused server class SoC / ASIC (datacenter focused) devices (SSD - DC, NIC, CPU, GPU - DC):

- Critical priority are devices with the ability to handle user plain text data

- Top priority are CPU SoCs

- Other examples include SmartNIC and accelerators

- Over time scope includes further data center devices

- SSD, HDD, BMC, DIMM

Explicitly out of scope is how silicon integration into backend work is performed such as:

- Foundry IP integration

- Physical design countermeasures

- Analog IPs

- Post manufacture test and initialization (OSAT)

- Certification

# Use Cases

The Silicon RoT use cases can be supported through the adoption of specific industry standards and association/consortium specifications. Refer to <u>Industry Standards and Association</u> <u>Consortium Specifications</u>.

In this version, Caliptra Silicon RoT desired capabilities address the basics of supply chain security use cases.

# Supply Chain Security

- **Mutable Code Integrity:** The objective here is to prove the device is running genuine firmware that the device manufacturer can vouch for its authenticity & integrity, and the device owner can ensure only authorized updates are applied to the device. This flow is aligned with [Reference 4] and can be achieved with dual signature verification of equal imposition.

- **Configuration & Lifecycle Management**: allow the platform owner to securely configure the RoT capabilities, and enable/authorize lifecycle state transitions of the SoC.

## **DICE-as-a-Service**

A Caliptra RTM exposes a "DICE-as-a-Service" API, allowing Caliptra to derive and wield a DICE identity on behalf of other elements within the SoC. Use-cases for this API includes serving as a signing oracle for an SPDM responder executing in the SoC Application Processor.

# Industry Standards and Association / Consortium Specifications

This specification follows the industry standards and specifications listed in References.

NIST SP800-193 Platform Firmware Resiliency

Per [<u>Reference 1</u>], RoT subsystems are required to fulfill three principles: *Protection, Detection* and *Recovery*. The associated RoT services are referred to as:

- **The Root of Trust for Update (RTU)** is responsible for authenticating firmware updates and critical data changes to support platform protection capabilities.

- The Root of Trust for Detection (RTD) is responsible for firmware and critical data corruption detection capabilities.

- **The Root of Trust for Recovery (RTRec)** is responsible for recovery of firmware and critical data when corruption is detected, or when instructed by an administrator.

These RoT services can be hosted by a complex RoT as a whole or it can be spread across one or more components within a platform. This determination has a basis in physical risk.

Physical adversaries with reasonable skill can bypass a discrete RoT's detection capabilities, for example, with SPI interposers.

However, an RoT embedded within an SoC or ASIC represents a much higher detection bar for a physical adversary to defeat. For this reason, a Caliptra Silicon RoT shall deliver the **Detection** (or Measurement) capability.

With the objectives of minimalistic scope for Silicon RoT and maximizing applicability and adoption of this specification, **Update** and **Recovery** are decoupled from Caliptra and are expected to be provided by an external RoT subsystem such as a discrete RoT board element on a datacenter platform. Because a physical adversary can trivially nullify any Recovery or Update capabilities, no matter where implemented, decoupling represents no regression in a security posture, while enabling simplicity and applicability for the internal SoC silicon RoT.

Detection of corrupted critical code & data (configuration) requires strong end to end cryptographic integrity verification. To meet the RTD requirements, Silicon RoT shall:

- Cryptographically measure its code & configuration

- Sign these measurements with a unique attestation key

- Report measurements to a host and/or external entity, which can further verify the authenticity & integrity of the device (a.k.a Attestation)

**Measurements** include **Code** and **Configuration**. Configuration includes invasive capabilities that impact the user SLA on Confidentiality -- for example, the enablement of debug capabilities that grant an operator access to raw, unencrypted registers for any tenant context. In order to measure and attest Configuration, the Silicon RoT must be in control of the Configuration.

As an extension to controlling Configuration, the Silicon RoT must control the security states (refer to <u>*Caliptra Security States*</u>). Certain security states by design grant full invasive capabilities to an external operator, for debug or field analysis.

Measurements must be uniquely bound to the device & its manufacturer to a minimum. This establishes the need for **Identity** services in the Silicon RoT, that serves as the basis for key derivation and attestation authenticity.

For further details about how Caliptra addresses NIST SP800-193, refer to Device Resilience.

## Trusted Computing Group (TCG) DICE Attestation

In accordance with OCP Attestation specification, devices must have a Cryptographic Identity for the endorsement of attestation quotes. The RTM implementation follows TCG DICE (refer to [Reference 6], [Reference 12] and [Reference 13]). One of the benefits of TCG DICE device identities is having renewable security. This renewability complements ownership transfer and circular economy. The new owner is not burdened with the identity of the previous owner, nor is the new owner burdened with trusting an irrevocable hardware identity certificate. This benefits the transferee, as their identities can be revoked through standard PKI mechanisms. DICE

based certificates are fully compatible with Public Key Infrastructure (PKI), including full life cycle management and PKI Certificate Revocation List (CRL).

Operational security during the manufacture process is critical, to ensure the DICE entropy is securely initialized, certified, and registered, avoiding any pilfering of this asset by eavesdroppers. Operational security is outside the scope of this specification.

# **Threat Model**

This section describes the Caliptra RoT threat model in terms of profile of the attacks and of the attackers that the Caliptra RoT is expected to defend against.

Threat model as described here takes into account attacker profile, assets and attack surfaces or paths to these assets based on attacker profiles. Following sections delve into each of these topics.

Threat scenarios as comprehended by assets & possible attack paths are as complete as possible but focus on the worst case scenarios. Thus not every attack path to asset is captured in this threat model.

# **Attacker Profiles**

Attacker profile is the outcome of following factors like tools accessible to the attacker, level of access to the target of evaluation & expertise of the attacker to use these methods. Next level of details of these capabilities scoped for this discussion are as follows.

## Tools Accessible to Attacker

| Attack Tools                                                                                                                                                                | Type of Attack                | Purpose/Usage                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Debuggers</li> <li>Fuzzing devices</li> <li>Image reverse<br/>engineering tools</li> <li>Software payloads</li> </ul>                                              | Logical Fault Injection       | <ul> <li>Find logical and<br/>functional vulnerabilities<br/>&amp; exploit those to<br/>achieve unauthorized<br/>operations</li> </ul> |

| <ul> <li>Clock fault injectors</li> <li>Voltage fault injectors</li> <li>Electromagnetic fault injectors</li> <li>Optical fault injectors</li> <li>Micro probing</li> </ul> | Environmental Fault Injection | <ul> <li>Alter execution flow of<br/>the critical decision<br/>points, especially in the<br/>early execution</li> </ul>                |

| <ul> <li>Power analyzers</li> <li>Timing analyzers<br/>(Scopes etc)</li> <li>Low speed bus<br/>analyzers</li> <li>Optical emission<br/>analyzers</li> </ul>                 | Side Channel Analysis         | <ul> <li>Infer security sensitive<br/>information by<br/>analyzing various<br/>operational conditions</li> </ul>                       |

|--|

## Level of Access to TOE

| Type of Access  | Levels of Access                                                                   | Attack Paths Available                                                     |

|-----------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Physical Access | Unrestricted access for physical<br>and logical attacks                            | <ul> <li>Chip invasive</li> <li>Chip non invasive</li> </ul>               |

|                 | Limited access for attacks with<br>both privileged & unprivileged<br>access rights | <ul> <li>Chip non invasive<br/>attacks</li> <li>Network attacks</li> </ul> |

# Definition of Expertise\* (JIL)

| Proficiency level | Definition                                                                                                                                                                                                                            | Detailed definition                                                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expert            | Can use chip invasive, fault<br>injections, side channel &<br>logical tools<br>Understands HW & SW in<br>depth<br>Familiar with implemented<br>• Algorithms<br>• Protocols<br>• HW structures<br>• Principle and<br>security concepts | <ul> <li>Familiar with<br/>developers knowledge<br/>namely algorithms,<br/>protocols, hardware<br/>structure, principles</li> <li>Techniques and<br/>tools for attacks</li> </ul> |

| Proficient        | Can use fault injections, side<br>channel & logical tools<br>Understands HW & SW in<br>reasonably<br>Familiar with security behavior                                                                                                  | Familiar with<br>• security behavior, classical<br>attacks                                                                                                                        |

# Types of Attacks

**Physical Attacks**

A physical attacker has full access to the electrical and physical components and interfaces/connectors/ports of the SoC/ASIC in which the Caliptra RoT is integrated without restriction.

Invasive attacks involving depackaging/delayering of the SoC/ASIC is out-of-scope.

Non-Invasive attacks are in-scope.

- Fault Injection attacks

- Counter measurements as strong recommendation

- Power and Electromagnetic analysis attacks

- Counter measurements as strong recommendation

| Attack                    | Description                                                                                          | Threat Model Scope                                                                                                         |

|---------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Electromagnetic – Passive | Attacker observes the<br>electromagnetic power<br>spectrum and signals<br>radiated from the product. | Includes all attacks at all<br>frequency ranges,<br>including radio frequencies,<br>infrared, optical, and<br>ultraviolet. |

|                           |                                                                                                      | Excludes attacks requiring removing the package lid.                                                                       |

| Electromagnetic – Active | Attacker directs<br>electromagnetic radiation at<br>the product or portions of<br>the product.                                                                          | Includes all attacks at all<br>frequency ranges,<br>including radio frequencies,<br>infrared, optical, and<br>ultraviolet. |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                                                                                                                         | Excludes attacks requiring removing the package lid.                                                                       |

| Electric – Passive       | Attacker probes the external<br>pins of the package and<br>observes electrical signals<br>and characteristics including<br>capacitance, current, and<br>voltage signal. | Includes both analog<br>attacks and digital signal<br>attacks.                                                             |

|                          |                                                                                                                                                                         | Excludes attacks requiring removing the package lid.                                                                       |

| Electric – Active        | Attacker alters the electrical signal or characteristics of external pins.                                                                                              | Includes both analog<br>attacks and digital signal<br>attacks.                                                             |

|                          |                                                                                                                                                                         | Excludes attacks requiring removing the package lid.                                                                       |

| Temperature – Passive    | Attacker observes the temperature of the product or portions of the product.                                                                                            | Excludes attacks requiring removing the package lid.                                                                       |

| Temperature – Active | Attacker applies external<br>heat sources or sinks to<br>alter the temperature of the<br>product, possibly in a rapid<br>fashion. | Includes all temperature<br>ranges (e.g. pouring liquid<br>nitrogen over the package<br>or heating the package to<br>above 100C) |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                                   | Excludes attacks requiring removing the package lid.                                                                             |

| Sound - Passive      | Attacker observes the sounds emitted by the product.                                                                              | Includes all frequencies.                                                                                                        |

|                      |                                                                                                                                   | Excludes attacks requiring removing the package lid.                                                                             |

Table 3: Attacks and Threats

Logical Attacks

| Attack                    | Description                                                               | Included / Excluded                                                                                   |

|---------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Debug/Register Interfaces | Manipulation of externally<br>accessible registers of the<br>Caliptra RoT | Includes all buses<br>accessible to components<br>external to Caliptra RoT<br>including JTAG and SMN. |

| Software Interfaces   | Attacker invokes software<br>interfaces exposed by the<br>Caliptra RoT to external<br>components. | Includes all externally<br>exposed software interfaces<br>from both non-RoT firmware<br>as well as interfaces<br>accessed by external IP<br>blocks.                                       |

|-----------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                                                   | Includes exploiting both design and implementation flaws.                                                                                                                                 |

|                       |                                                                                                   | For High Value Assets only<br>(see next subsection), the<br>attacker is assumed to fully<br>control all mutable code of<br>the SoC, including<br>privileged Caliptra RoT<br>mutable code. |

| Side channel - Timing | Attacker observes the elapsed time of different sensitive operations.                             | Includes attacks where the<br>attacker actively stimulates<br>the sensitive operations<br>while timing.                                                                                   |

| Cryptographic Analysis | Attacker observes plaintext,<br>ciphertext, related data, or<br>immediate values in<br>cryptography to overcome<br>cryptographic controls | Includes all practical<br>cryptanalysis attacks.<br>Assumes NIST-unapproved<br>algorithms provide no<br>security. (e.g. SHA-1, Single<br>DES, ChaCha20) |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                                           | Assumes any cryptographic<br>algorithm that provides less<br>than 128 bits of security (as<br>determined by NIST SP<br>800-57) provides no<br>security. |

|                        |                                                                                                                                           | Excludes quantum<br>computer attacks. This<br>exclusion will be removed<br>soon.                                                                        |

Table 4: Logical Attacks

# **Trust Boundaries**

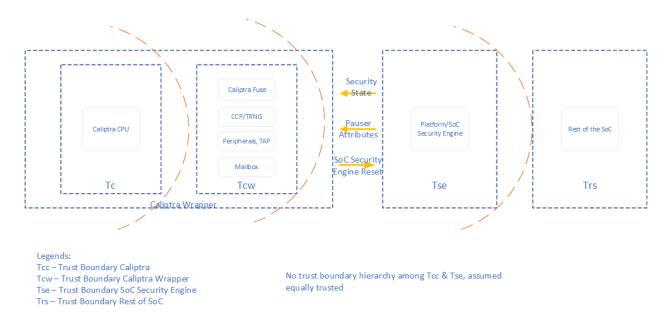

Following diagram establishes trust boundaries for the discussion of threat modeling. Caliptra based SoCs are expected to have Caliptra as silicon RoT, platform or SoC security engine to orchestrate SoC security needs & rest of the SoC.

Trust levels of Caliptra and the SoC security engine are not hierarchical. These two entities are responsible for different security aspects of the chip.

# Caliptra Assets & Threats

Assets are defined to be secrets or abilities that must be protected by an owner or user of the asset. Ownership means that the owner has the responsibility to protect these assets and must only make them available based on a defined mechanism while protecting all other assets. An example of when an owner must protect assets would be moving from secure mode to unsecure. Another example would be moving from one owner to another. Before moving through these transitions, the owner will need to ensure all assets are removed, disabled or protected based on use-case definition.

| Asset<br>Category                     | Asset                         | Security<br>Property                 | Attacker<br>Profile                                                           | Attack Path                                                             | Mitigation                                                                 |

|---------------------------------------|-------------------------------|--------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Fuse/OT<br>P high<br>value<br>secrets | UDS Seed                      | Confidenti<br>ality and<br>Integrity | nd .                                                                          | Malicious<br>manufacturing<br>spoofing on UDS<br>seeds                  | UDS<br>obfuscation/encrypti<br>on with class RTL<br>key                    |

|                                       |                               |                                      |                                                                               | Invasive attack<br>(fuse analysis)                                      | Shield fuse IP                                                             |

|                                       |                               |                                      |                                                                               | Boot path<br>tampering while<br>retreving UDS<br>values                 | UDS<br>obfuscation/encrypti<br>on with class RTL<br>key                    |

|                                       |                               |                                      | Expert                                                                        | Attempting to<br>derive die specific<br>keys by knowing<br>UDS, KDF     | Confine<br>unobfuscated UDS<br>& subsequent<br>derivations to key<br>valut |

|                                       | Entropy ality an              | Confidenti<br>ality and<br>Integrity | Expert                                                                        | Malicious<br>manufacturing<br>spoofing on field<br>entropy              | Field entropy<br>obfuscation/encrypti<br>on with class RTL<br>key          |

|                                       |                               |                                      |                                                                               | Invasive attack<br>(fuse analysis)                                      | Shield fuse IP                                                             |

|                                       |                               |                                      |                                                                               | Boot path<br>tampering while<br>retreving field<br>entropy values       | Field entropy<br>obfuscation/encrypti<br>on with class RTL<br>key          |

|                                       |                               | Expert                               | Attempting to<br>derive die specific<br>keys by knowing<br>field entropy, KDF | Confine field<br>entropy &<br>subsequent<br>derivations to key<br>valut |                                                                            |

|                                       | FW<br>authenticat<br>ion keys | Integrity                            | Proficient                                                                    | Glitching                                                               | 1. Redundant<br>decision making on<br>critical code<br>execution           |

|                         |                                                                       |                                      |            |                                                                                                                  | <ul><li>2. Error check</li><li>before consuming</li><li>values from fuse</li><li>3. Environmental</li><li>monitoring &amp;</li><li>protection</li></ul> |

|-------------------------|-----------------------------------------------------------------------|--------------------------------------|------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Versioning<br>information<br>from fuses                               | Integrity                            | Proficient | Glitching                                                                                                        | Environmental<br>monitoring &<br>protection                                                                                                             |

|                         | IDEVID<br>CERT<br>chain                                               | Integrity                            | Proficient | Glitching                                                                                                        | <ol> <li>Environmental<br/>monitoring &amp;<br/>protection</li> <li>Error check<br/>before consuming<br/>values from fuse<br/>various ways</li> </ol>   |

| Die<br>unique<br>assets | UDS<br>(802.1AR<br>Unique<br>Device<br>Secret)                        | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key valult, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                                                   |

|                         | DICE UDS<br>(DICE<br>Unique<br>Device<br>Secret)                      | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key valult, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                                                   |

|                         | CDI0<br>(DICE<br>component<br>device<br>identifier<br>for Layer<br>0) | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key valult, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                                                   |

|                         | CDI1-n<br>((DICE<br>component<br>device                               | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel</li> </ol>                                | <ol> <li>Secrets locked in<br/>key valult, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                                                   |

|                               | identifier<br>for Layer<br>x) |                                      |            | attack to infer<br>secret                                                                                        |                                                                                                                                  |

|-------------------------------|-------------------------------|--------------------------------------|------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                               | IDevID_Pri<br>v               | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key vault, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                             |

|                               | LDevID_Pr<br>iv               | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key vault, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                             |

|                               | Obfuscatio<br>n Key           | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key vault, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                             |

|                               | Alias_Key<br>_Priv            | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key vault, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                             |

|                               | Alias_Key<br>_Priv            | Confidenti<br>ality and<br>Integrity | Proficient | <ol> <li>Software<br/>reading actual<br/>secrets</li> <li>Side channel<br/>attack to infer<br/>secret</li> </ol> | <ol> <li>Secrets locked in<br/>key vault, not<br/>readable by SW</li> <li>SCA protections</li> </ol>                             |

| Root of<br>trust<br>execution | ROM FW                        | Integrity                            | Proficient | Glitching                                                                                                        | <ol> <li>Redundant<br/>decision making on<br/>critical code<br/>execution</li> <li>Environmental<br/>monitoring &amp;</li> </ol> |

|                                                         |                                                                                          |                                                     |            |                                                                                                                                                                                                                                               | protection                                                                                                                                                      |

|---------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | Execution<br>of<br>unauthoriz<br>ed runtime<br>FW                                        | Authenticit<br>y &<br>Integrity                     | Proficient | Modify boot media                                                                                                                                                                                                                             | Authenticity &<br>integrity check<br>using PKI DSA<br>upon power on                                                                                             |

|                                                         | Execution<br>of<br>unauthoriz<br>ed runtime<br>FW                                        | Authenticit<br>y &<br>Integrity                     | Proficient | Arbitrary payload<br>pushed into<br>execution                                                                                                                                                                                                 | Authenticity &<br>integrity check<br>using PKI DSA<br>during software<br>updates & power on                                                                     |

|                                                         | Rollback<br>Attack                                                                       | Versioning                                          | Proficient | <ol> <li>Modify boot<br/>media to host older<br/>versions</li> <li>Bypass version<br/>check during boot</li> </ol>                                                                                                                            | 1. Authenticity &<br>integrity check<br>using PKI DSA<br>upon power on<br>2. Failproof, audited<br>boot code<br>implementation<br>responsible to load<br>images |

|                                                         | Control<br>flow                                                                          | Integrity &<br>Confidenti<br>ality if<br>applicable | Proficient | <ol> <li>Return &amp; jump<br/>addresses<br/>manipulation</li> <li>Return values,<br/>errors tampering</li> <li>Stack overflow</li> <li>Buffer overflows</li> <li>Privilege<br/>escalations &amp;<br/>highjacking</li> <li>etc/tbd</li> </ol> | Various control flow<br>integrity measures<br>Secure coding<br>practices and<br>auditing<br>implementation                                                      |

| Boot<br>measure<br>ments<br>protected<br>by<br>Caliptra | Boot<br>Measurem<br>ents that<br>Caliptra as<br>RTM<br>gathers,<br>stores and<br>reports | Integrity                                           | Expert     | <ol> <li>Manipulate<br/>measurements</li> <li>AiTM while in<br/>transit to Caliptra</li> <li>SoC sends<br/>manipulated<br/>measurements to<br/>Caliptra</li> </ol>                                                                            |                                                                                                                                                                 |

| Caliptra<br>inputs | Security<br>state                                       | Integrity | Proficient | Glitching                                                                                                                                                                                                                                                                           | Environmental<br>monitoring &<br>protection              |

|--------------------|---------------------------------------------------------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                    | Mode<br>selection<br>(active,<br>passive<br>selections) | Integrity | Proficient | Glitching                                                                                                                                                                                                                                                                           | Environmental<br>monitoring &<br>protection              |

|                    | Pauser<br>Attribute                                     | Integrity | Proficient | Glitching                                                                                                                                                                                                                                                                           | Environmental<br>monitoring &<br>protection              |

|                    | JTAG<br>debug                                           | Integrity | Proficient | 1. Attempt to<br>manipulate RoT<br>execution via JTAG<br>to non POR flows<br>2. Attempt to<br>retrieve device<br>secrets via JTAG<br>when product is<br>field-deployed<br>3. Attempt to<br>retrieve device<br>secrets via JTAG<br>when product is<br>under<br>development/debu<br>g | Implement security<br>mode management<br>within Caliptra |

Table 2: Assets

# **High Level Architecture**

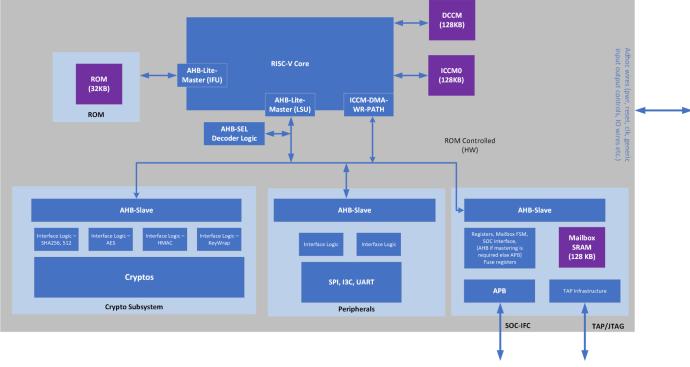

A Caliptra RTM subsystem has the following basic, high-level blocks:

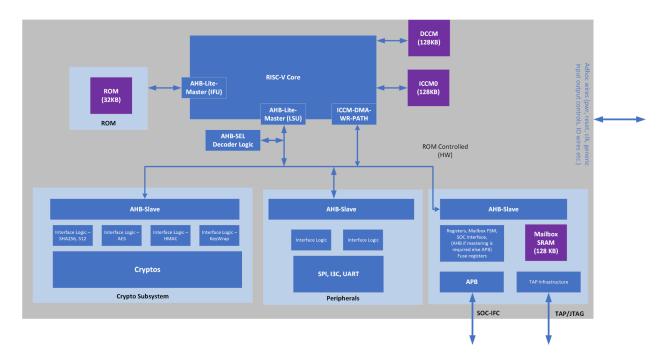

See details in <u>HW Section</u>.

# **Caliptra Profiles**

Caliptra supports two modes of integration with different security postures and FW loading flows. The first is Active Profile (AP) where Caliptra loads its FW directly from persistent storage (eg. SPI) while in Passive Profile (PP) Caliptra FW is being pushed into mailbox SRAM buffer by SoC immutable code (HW or ROM) controlling persistent storage.

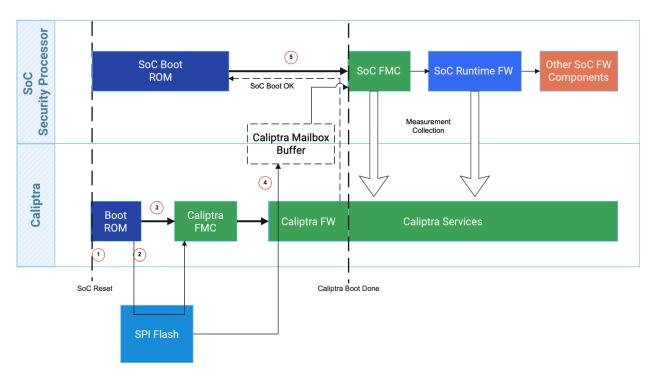

## Active Profile

When Caliptra is integrated into an SOC in AP mode, Caliptra RTM is the first uncore microcontroller taken out of reset with direct access to persistent storage. The flow for boot is as follows:

- 1. Hardware executes SOC power-on reset logic.

- 2. Caliptra ROM executes first and performs cryptographic identity generation, reads in Caliptra firmware from flash.

- 3. Caliptra ROM measures and verifies its firmware before loading/executing it. Refer to <u>Error Reporting and Handling</u> for details regarding FMC verification failures.

- 4. After loading its own firmware, Caliptra copies the SOC First Mutable Code (FMC) into an SOC internal SRAM mailbox buffer and measures that firmware.

- 5. At this point, Caliptra may signal to SOC ROM and SOC uncore to continue power-on reset as shown in Figure 1.

Figure 1: AP Boot Flow

In the AP profile, the Caliptra trusted computing base (TCB) for integrity of Core Root of Trust measurement is the Caliptra security controller and ROM. The verification of measurement includes:

- 1. The SOC design ingests firmware through Caliptra

- 2. Caliptra IP, Caliptra ROM, and Caliptra Firmware

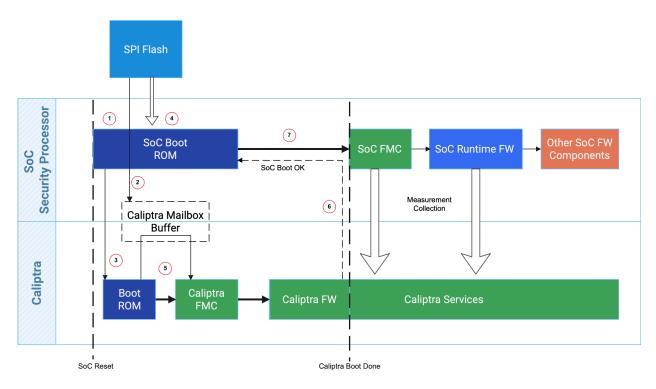

#### Passive Profile

To facilitate ease of integration and reliable measurement, the Caliptra RTM is the first uncore controller to be taken out of reset by the SoC ROM. Once loaded, it provides callback signals for the remaining SoC subsystem to resume normal reset flow.

All firmware that is loaded from an outside entity (and subsequently executed on the microprocessor) shall be considered untrusted; this firmware's measurements shall be reported to the Caliptra RTM before it is allowed to run within the SoC.

In the PP profile, the Caliptra trusted computing base (TCB) for integrity of Core Root of Trust measurement is the Caliptra security controller and SoC ROM. The verification of measurement mechanism includes:

- 1. Hardware executes SOC power-on reset logic.

- 2. SOC ROM executes, reads Caliptra firmware into Mailbox SRAM buffer.

- 3. SOC ROM signals Caliptra for its ROM to execute

- 4. SOC ROM pauses and waits for a signal (resume) from Caliptra

- 5. Caliptra ROM cryptographically authenticates its FW, measures and (if valid) executes its FW and then derives cryptographic identities

- 6. Caliptra signals back to SOC to resume reset.

- 7. SOC reads in its firmware, cryptographically authenticates its FW and provides measurements to Caliptra before executing.

Refer to <u>Error Reporting and Handling</u> for details regarding Caliptra and SoC firmware load and verification error handling.

## Figure 2: PP Boot Flow

The PP profile is less intrusive to integrations, but extends the TCB for Caliptra to include SOC ROM. The verification of measurement mechanism integration includes:

- 1. The SOC design that executes SOC power-on reset logic.

- 2. SOC ROM, SOC boot controller

- 3. Caliptra IP, Caliptra ROM, and Caliptra Firmware.

4. SOC first mutable code.

The trusted computing base for the SOC is larger in PP, but simplifies integration while preserving many of the Caliptra security guarantees.

## Identity

A Caliptra RTM must provide its runtime code with a cryptographic identity in accordance with the TCG DICE specification. This identity must be rooted in ROM, and provides an attestation over the security state of the RTM as well as the code that the RTM booted.

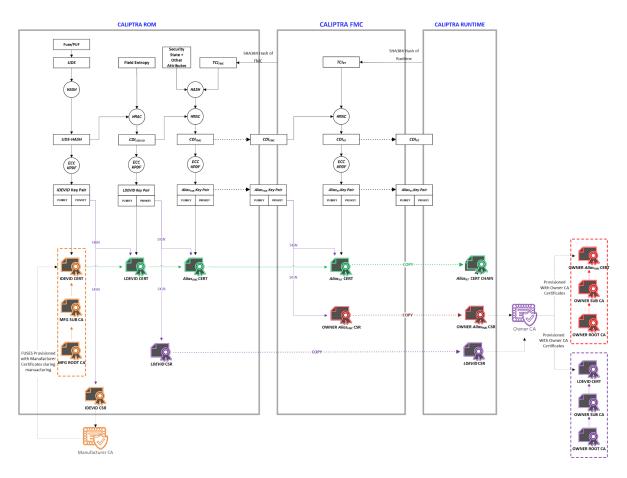

Figure 3: DICE Cert/Key Generation

### UDS

A combination of mask ROM and HW macros must implement the DICE key derivation and power-on latch, hiding the UDS and making only the CDI-derived signing key visible to firmware.

The Caliptra UDS is stored in fuses, and is encrypted at rest by an obfuscation secret<sup>2</sup> known only to Caliptra. The UDS, once read by Caliptra ROM at boot, is then used to derive the IDevID identity.

#### IDevID key

A Caliptra RTM's IDevID key is a hardware identity generated by Caliptra ROM during manufacturing. This key must be solely wielded by Caliptra ROM, and shall never be exposed externally at any phase of the Caliptra life cycle. IDevID is used to endorse LDevID. See <u>below</u> for further details on IDevID provisioning.

<sup>&</sup>lt;sup>2</sup> This obfuscation secret may be a chip-class secret, or a chip-unique PUF, with the latter preferred.

#### LDevID key

While it is recommended that implementations of Caliptra add physical attack countermeasures to protect fuses from imagery SDC attacks, SoC fuses generally have varying levels of resistance to physical attackers. While it is important to protect device security assets with physical attack countermeasures, a good design principle is to assume compromise. Renewable security, often referred to as trusted computing base recovery, is a base design principle in the Caliptra RTM. To mitigate the risk of UDS compromise for devices that may have been exposed to sustained physical attack in the supply chain, Caliptra RTMs shall support field-programmable entropy which factors into the device's LDevId identity. The LDevId identity is endorsed by IDevID and in turn endorses the FMC Alias key.

Caliptra's field-programmable entropy shall consist of at least four 32-byte slots. An owner may decide to program as few or as many slots as they wish. Upon programming new entropy, on next reset the device will begin wielding its fresh LDevID. Owners will need to validate the new LDevID by way of IDevID.

Note that LDevID is intended to hedge against the event that a supply-chain attacker has obtained UDS - and by extension, IDevID<sub>priv</sub>. Therefore, IDevID's endorsement of LDevID should not be the sole signal to a user that LDevID is trustworthy. Owners should also work to ensure that their device onboarding flow - wherein field entropy is provisioned and LDevID is registered - is resistant to remote man-in-the-middle attackers that may attempt to use a previously-exfiltrated UDS to register a forged LDevID.

#### FMC alias key

The LDevID CDI is mixed with a hash of FMC, as well as the security state of the device, via a FIPS-compliant HMAC, to produce  $CDI_{FMC}$ . ROM uses  $CDI_{FMC}$  to derive the Alias<sub>FMC</sub> keypair. ROM wields LDevID to issue a certificate for Alias<sub>FMC</sub>. The Alias<sub>FMC</sub> certificate includes measurements of the security state and FMC. ROM makes  $CDI_{FMC}$ , Alias<sub>FMC</sub>, and its certificate, available to FMC.

FMC wields  $Alias_{FMC}$  to issue a CSR for  $Alias_{FMC}$ . FMC then mixes  $CDI_{FMC}$  with a hash of runtime firmware to produce  $CDI_{RT}$ . FMC uses  $CDI_{RT}$  to derive the  $Alias_{RT}$  alias keypair. FMC wields  $Alias_{FMC}$  to issue a certificate for  $Alias_{RT}$ . This alias certificate includes measurements of runtime firmware. FMC makes  $CDI_{RT}$ ,  $Alias_{RT}$ , its certificate, available to application firmware, while withholding  $CDI_{FMC}$  and  $Alias_{FMC}$ .

#### Security state

Devices may support features like debug unlock or JTAG. These features, when enabled, significantly alter the security state of the device. The configuration of these features shall be captured in the device's DICE identity. The security state shall be captured as an input to the FMC's CDI, and represented within the FMC's alias certificate.

#### Owner endorsement

Caliptra RTM firmware shall be signed by the vendor. In addition, this firmware may also be signed by the owner when ownership control is enforced. If a second signature is present for ownership enforcement, Caliptra must extract the owner's public key from the firmware image during cold boot, and latch the owner key into Caliptra's RAM for the remainder of its uptime<sup>3</sup>. Caliptra will then use both the vendor key and owner key to verify hitless firmware updates.

Caliptra shall attest to the value of the owner key, enabling external verifiers to ensure that the correct owner key has been provisioned into the device. Caliptra shall do so by including the owner key as an input to the FMC's CDI (as part of "other attributes" from Figure 3 above), and represent it within the FMC's alias certificate.

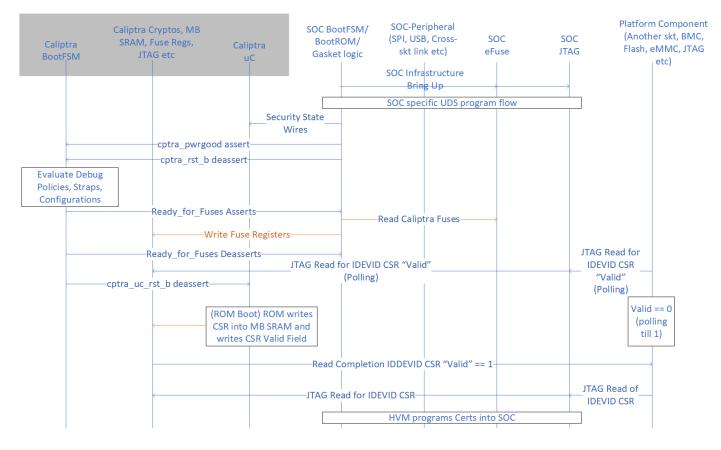

## Provisioning IDevID during manufacturing

#### Figure 4: Device Manufacturing Identity Flow

1. High Volume Manufacturing programs NIST compliant UDS into fuses using SOC specific fuse programming flow. Note that this UDS goes through an obfuscation function within Caliptra IP. Hence it is fine for HVM to generate the UDS.

<sup>&</sup>lt;sup>3</sup> This memory should only be volatile in the face of a power loss event. See details in <u>HW Section</u>.

- 2. SOC will drive the security state indicating that its a manufacturing flow. Refer to "Caliptra Security States" for encodings

- 3. SOC will follow the boot flow as defined in Caliptra IP HW boot flow to assert cptra\_pwrgood & deassert cptra\_rst\_b, followed by writing to the fuse registers.

- 4. HVM must now poll for "CSR Valid" bit available as Caliptra IP hardware register over JTAG

- 5. ROM will look at the manufacturing state encoding & populates the Caliptra internal SRAM [MB SRAM hardware structure is reused] with the CSR and write to Caliptra internal register to indicate CSR is valid (refer to Caliptra ROM spec & Identity section in this document on the ROM steps to generate the CSR)

- 6. HVM polling reads through JTAG will see that CSR is valid at this point

- 7. HVM must now read the CSR over JTAG

- 8. HVM must write a bit over JTAG that it has completed reading CSR

- 9. Caliptra IP HW will now open up the Caliptra Mailbox for SOC usages such as FW loading (if required in some HVM flows)

- a. Note that until the above write is complete, SOC will not get a grant/lock of the APB-exposed mailbox interface.

#### Certificate Format

Device Identity Certificates are following X.509 v3 format described in RFC 5280. The values in the X.509 certificate shall follow the DICE TCBInfo fields, as defined in [12]. The owner public key shall be extended into VendorInfo, with the security operational state reflecting the flags of DICE TCBInfo. Additional fields may be extended into VendorInfo.

[**TODO for 0.8 release**: The x509 owner key, JTAG state, public key used to verify firmware should be extended in the Cert. ]

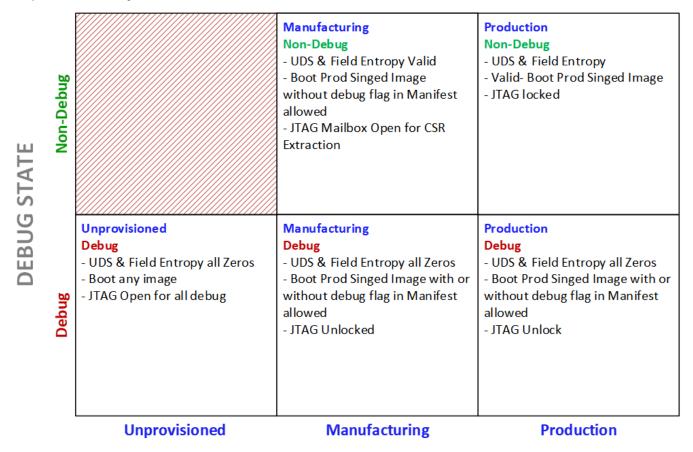

#### Caliptra Security States

## LIFECYCLE STATE

#### Figure 5: Caliptra Security States

#### Definitions

- **DebugLock:** Caliptra JTAG is NOT open for uController & HW debug

- **DebugUnlock:** Caliptra JTAG is open for uController & HW debug

- Unprovisioned: Blank/unprogrammed fuse part

- **Manufacturing:** Device is going through manufacturing flow where High-Volume-Manufacturing (HVM) Caliptra fuses are being programmed

- Production: All Caliptra's HVM Fuses are programmed.

#### Notes:

- Caliptra' security state is determined by the SOC's security state and SOC device lifecycle state.

- Caliptra's state is considered a mode of operation

- Caliptra security state is defined by the upper most bit of the encoding below; 1=DebugLocked & 0=DebugUnlocked

- Lower 2 bits are mapped to device lifecycle (Unprovisioned, Manufacturing, Production)

- SOC's security state may also be influenced by its own device life cycle.

- Caliptra's security state determines Caliptra's debug state and the state of its security assets.

- In general, if Caliptra is in unsecure state, all keys, assets are 'zeroized'. Zeroized may mean switching to all 0s or 1s or debug keys based on the key. Refer to <u>Caliptra Assets</u> for a description of Caliptra assets.

| {Security<br>State, Device<br>Life Cycle<br>State[1:0]} | State                               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | State Transition<br>Requirement                                                                                                          |

|---------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 000b                                                    | DebugUnlocked<br>&<br>Unprovisioned | <ul> <li>This is Caliptra's default state; it is used for development and early Caliptra bring up. This state is not used to provision the Caliptra assets. In this state:</li> <li>UDS and all other identity critical assets shall not be not programmed in fuses. Unprogrammed Fuse bits shall be read as 0s (zero). <ul> <li>The debug UDS shall be obfuscated and de-obfuscated using the debug obfuscation key.</li> </ul> </li> <li>Obfuscation key: The debug obfuscation key shall be used</li> <li>Caliptra JTAG is unlocked and allows microcontroller debug</li> <li>Caliptra JTAG can access IP internal registers through FW or directly</li> </ul> | Unprovisioned to any<br>other state required<br>cold boot cycle of<br>Caliptra & SOC                                                     |

| 100b                                                    | DebugLocked<br>&<br>Manufacturing   | UDS and other identity critical assets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Manufacturing -><br>Unsecure State<br>transition possible<br>without power cycle<br>and Caliptra will clear<br>all the security critical |

|      |                                  | <ul> <li>shall be used)</li> <li>Caliptra JTAG shall be locked –<br/>microcontroller debug shall be disabled</li> <li>Caliptra microcontroller can be<br/>interrupted through JTAG mailbox</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       | assets/registers before<br>JTAG is opened<br>Manufacturing -><br>Secured state possible<br>ONLY with a power<br>cycle<br>Refer to <u>Provisioning</u><br><u>During Manufacturing</u><br>for details on<br>manufacturing and<br>provisioning details. |

|------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101b | DEDUYLUCKEU                      | <ul> <li>All security assets are in production mode. In this state:</li> <li>Production UDS and obfuscation key shall be used.</li> <li>CPU execution shall be enabled</li> <li>All 'backdoor' functionality shall be disabled (e.g., developer functions/functionality that could reveal sensitive information or result in escalation of privileges, etc.)</li> <li>Debug functions shall be disabled <ul> <li>Caliptra JTAG is locked – microcontroller debug shall be disabled</li> <li>Caliptra microcontroller shall not be interruptible through JTAG mailbox</li> </ul> </li> </ul> | DebugLocked -><br>Debug Unlocked<br>possible without power<br>cycle and Caliptra will<br>clear all the security<br>critical assets/registers<br>before JTAG is opened                                                                                |

| 011b | DebugUnlocked<br>&<br>Production | <ul> <li>This state is used when debugging of Caliptra RTM is required. When in this state:</li> <li>UDS and other identity critical assets are programmed into Fuses. They may not have been written into Caliptra fuse registers if the unsecure state entered before Caliptra is out of reset. If unsecure state transition happened after fuses are written to Caliptra, they are cleared on seeing the security state</li> </ul>                                                                                                                                                       |                                                                                                                                                                                                                                                      |