Raspberry Pi 5: Schnelleres USB und 5-Volt-Toleranz

Die Raspi-Entwickler geben weitere Details zum I/O-Chip RP1 preis. In ihm könnten auch noch versteckte Funktionen schlummern.

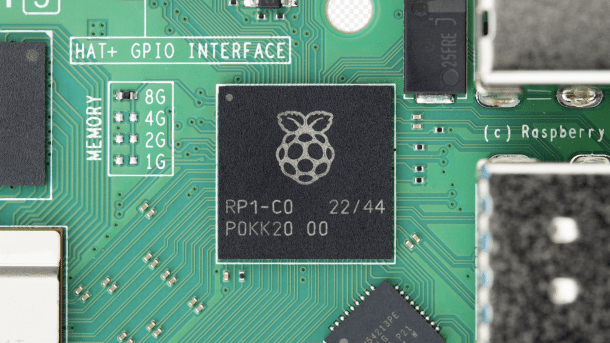

(Bild: Raspberry Pi Ltd.)

Zu den größten Neuerungen des Raspberry Pi 5 zählt sein I/O-Chip RP1, der allerlei Anschlüsse bereitstellt und Analogsignale verarbeitet. In einem ersten Datenblatt verrät die Raspberry Pi Ltd. weitere Details zum RP1, begleitet von einem kurzen Blog-Beitrag und einer Diskussionsrunde zwischen Entwicklern. In den Halbleiterbaustein flossen mehr als sieben Jahre Entwicklungszeit.

Ein großes Upgrade zum vorherigen Raspi 4 mit BCM2711 und separatem USB-Controller gibt es etwa bei USB 3.0: Der neue RP1 integriert zwei Controller, die jeweils einmal USB 3.0 und USB 2.0 beherrschen. Beide 3er-Anschlüsse können parallel ihre volle Geschwindigkeit von 5 Gbit/s erreichen.

Mehr MIPI-Flexibilität

Alle Funktionen des Mobile Industry Processor Interface (MIPI) sind beim Raspi 5 über zwei Anschlüsse und ohne Compute-Modul verfügbar. Beide übertragen jeweils 8 Gbit/s, verteilt auf je vier Lanes. Sie empfangen beide wahlweise Kamerabilder oder geben ein Display-Signal aus. So kann man wahlweise zwei Kameras oder zwei Displays oder jeweils eins davon anschließen. Beim Raspi 4 gibt es ohne zusätzliches Compute-Modul fest verschaltet je zwei Lanes für eine Kamera und ein Display.

Außerdem sitzen im RP1 zwei ARM-Kerne vom Typ Cortex-M3, die sich unter anderem um die Initialisierung beim Boot-Prozess kümmern.

Wer etwa mit Steckboards – sogenannten Breadboards – bastelt, hat Grund zur Freude: Die GPIO-Pins sind jetzt offiziell 5-Volt-tolerant. Das hilft beispielsweise beim Einsatz alter Sensoren, die mehr als 3,3 Volt benötigen. Beim Raspi 4 lief man ohne Umwege (etwa mit externen Dioden) Gefahr, dass die GPIO-Pins wegschmoren.

(Bild: Raspberry Pi Ltd.)

Drei Revisionen

Vom RP1-Chip gibt es drei Revisionen: A0, B0 und C0. Letztere kommt auf den finalen Raspi-5-Boards zum Einsatz. Auf dem Weg dahin haben die Entwickler den RP1 in programmierbaren Logikchips (FPGAs) emuliert. TSMC fertigt die RP1-Chips inzwischen mit 40-Nanometer-Technik (40LP-Prozess).

Vorserienchips hat die Raspberry Pi Ltd. auf PCI-Express-Karten gepackt und in verschiedenen Systemen getestet, darunter der Raspi 4, später der Raspi 5, aber auch Desktop-PCs mit x86-Prozessoren. Auf den finalen Raspi-5-Boards ist der RP1 fest aufgelötet und über vier PCIe-2.0-Lanes mit Broadcoms BCM2712-SoC verbunden.

Der Raspi-Schöpfer, Eben Upton, erklärt im Blog, dass die Dokumentation zum RP1 vorläufig und primär für Treiberentwickler gedacht ist. Weitere Details sollen in Zukunft offengelegt werden – im Chip könnten also weitere Funktionen schlummern. Jetzt schon dokumentiert ist etwa ein Analog-Digital-Wandler (ADC) mit 12 Bit Auflösung und 500 KSamples/s, der anscheinend aber beim Raspi 5 nicht über die GPIO-Pins erreichbar ist.

Empfohlener redaktioneller Inhalt

Mit Ihrer Zustimmmung wird hier ein externer Preisvergleich (heise Preisvergleich) geladen.

Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit können personenbezogene Daten an Drittplattformen (heise Preisvergleich) übermittelt werden. Mehr dazu in unserer Datenschutzerklärung.

(mma)