Neuer VISC-Prozessor von Soft Machines

Der 64-Bit-Shasta-Prozessor mit "inversed Hyperthreading" und mit 2 GHz Takt soll 2016 herauskommen.

Das kalifornische Startup Soft Machines hat nachgelegt. Nach dem ersten VISC-Testchip mit 500 MHz Takt, der aber nur als "Proof-of-Concept" gedacht war, stellte Firmenchef Mohammad Abdallah nun auf der Linley Processor Conference in Santa Clara den ersten richtigen VISC-Prozessor Shasta vor.

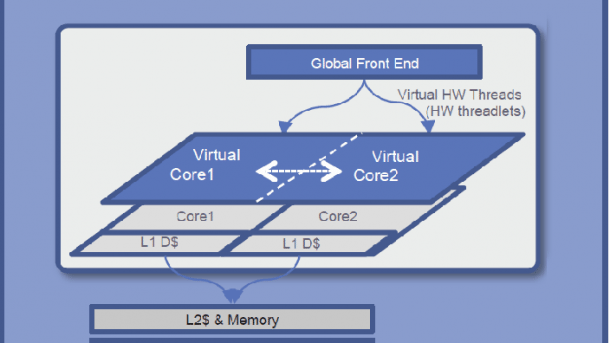

Der in 16-nm-TSMC-Prozess gefertigte Chip läuft mit 64 Bit, mit 2 GHz und mit 1 MByte L2-Cache pro Kern. Er soll dank der VISC-Architektur seine beiden Kerne gleichzeitig an Single-Thread-Jobs arbeiten lassen. Die VISC-Architektur zerlegt den Job in kleine sogenannte Threadlets, die parallel laufen können. Aufs diese Weise kann die Architektur laut Soft Machines zwei- bis dreimal mehr Instruktionen pro Takt ausführen als klassische Architekturen. Gleichzeitig soll sie dank niedrigerem Takt sehr energieeffizient sein -- bis hin zu Faktor 4 in der Disziplin Performance pro Watt. Daher peilt Soft Machines vor allem den Mobile-Markt an.

VISC ist dabei nicht auf einen bestimmten gastgebenden Instruktionssatz beschränkt, der Virtual Software Layer kann x86, ARM oder andere Instruktionssätze in Threadlets zerlegen, die die Kerne dann ausführen. Wie kompatibel das Ganze ist, mit all den Interrupts, Exceptions, Privileg-Level und so weiter, muss man noch sehen. Immerhin läuft aber unter x86 (64 Bit) ein Ubuntu 14.04.2 mit gcc 4.7 und mit den nicht ganz trivialen SPEC-CPU2006-Benchmarks. Shasta lässt sich aber auch mit nativen VISC-Code füttern, was wahrscheinlich noch effizienter ist.

(Bild: Soft Machines)

Der Shasta-Prozessor kann seine beiden physischen Kerne völlig unabhängig voneinander laufen lassen oder als einen einzigen virtuellen Kern -- genau umgekehrt wie bei Hyperthreading, weshalb man auch gern von inversem Hyperthreading spricht.

SPEC-Benchmarks

Die Effizienz von Shasta gibt Soft Machines in Vergleich mit verschiedenen 2-Wide-, 3-Wide-, 5-Wide- und 8-Wide-OOO-Architekturen an, alle bei 2 GHz Takt (ohne Turbo) und irgendwie normiert auf 16-nm-Design-Größe und bei verschiedenen Energieverbrauchspunkten der CPU (nicht TDP, sondern beim Benchmark-Lauf gemessen).

(Bild: Soft Machines)

Als Benchmark wird der geometrische Mittelwert der beiden SPEC-CPU2006-Suiten herangezogen, 32bittig kompiliert mit gcc 4.6/4.7 ohne Autoparallelisierung. Mit OOO-Width meint Soft Machines offenbar die Maximalzahl der pro Takt an die Funktionseinheiten verteillbaren Instruktionen, besser bekannt als "Issue Width". 2-Wide wäre dann wohl Atom, 3-Wide ein ARM Cortex A15, 5-Wide müsste ein Cortex A53 oder ein Apple A7/8 sein (obwohl letzterer gemeinhin als 6-Wide betrachtet wird). 8-Wide trifft auf den Haswell-Prozessor mit seinen 8 Ports zu. Soft Machines zeigt in der Grafik auch noch hochgerechnete Punkte, an denen hypothetische, klassische Prozessoren liegen würden, wenn sie zwei Kerne irgendwie an einem Thread werkeln lassen könnten, bei etwa doppelter Energieaufnahme und maximal doppelter Performance. Auch in diesem Fall zeigt sich Shasta als effizienter.

Entwicklungssysteme mit Shasta sollen im nächsten Jahr verfügbar sein. Auch eine Dual-Prozessor-Version ist vorgesehen. Daneben ist für den Embedded Markt ein SoC "Mojave" mit zwei Shasta-Prozessoren, GPU (Imagination Tech), DDR4-Speicher, PCIe, USB, Netzwerk, Audio und so weiter geplant, das ebenfalls 2016 herauskommen soll.

Soft Machines will den Prozessor aber nicht selbst vermarkten, sondern hofft auf Lizenznehmer. Interessante Investoren hat die Firma ja, etwa Samsung, AMD, Globalfoundries und andere. (as)