Dojo: Tesla baut mit (fast) ganzen Wafern eigene Riesen-KI-Prozessoren

Selbstentworfene Trainings-CPUs mit massenweise SRAM-Speicher anstelle von Nvidias A100-GPUs: Tesla legt die Grundlage für eigene Exascale-Supercomputer.

(Bild: Tesla)

"Projekt Dojo" geht bei Tesla in die heiße Phase. Der Autohersteller hat komplett eigene KI-Prozessoren entworfen, die in den nächsten Jahren die zugekaufte Hardware ablösen sollen – allen voran Nvidias GPU-Beschleuniger A100. Das Ziel: Hardware, die genau das kann, was man braucht, und das sehr gut ohne jeglichen Ballast. Dazu setzt Tesla auf moderne 7-Nanometer-Strukturbreiten, ausgeklügelte Packaging-Technik und einen ungeahnt hohen Grad an Integration.

Die Basis bildet ein 645 mm² großer Chip namens D1 mit etwa 50 Milliarden Transistoren. Darin sitzen 354 Cluster bestehend aus jeweils einem einzelnen CPU-Kern, begleitet von einer vierfach weiten Skalar- und einer doppelt weiten Vektoreinheit, die nur eine Aufgabe hat: haufenweise Matrizen berechnen. Vierfaches Simultaneous Multithreading (SMT, vier Threads pro CPU-Kern) soll die Auslastung maximieren.

Videos by heise

Die Vorstellung erfolgte im Rahmen des Tesla AI Day (im Video ab 1:45:35).

Massig Speicher und viel Rechenleistung

Dem Ganzen stehen 1,25 MByte SRAM pro Cluster und integrierte Switches zur Seite. Das ergibt pro CPU 354 Rechenkerne, 1416 Threads, 442,5 MByte flottes SRAM und 362 TeraFlops Rechenleistung im KI-Datenformat BF16 bei einer Leistungsaufnahme von 400 Watt. Alternativ beherrscht der D1 das neue Datenformat CFP8 (configurable Floating Point), FP32, INT32, INT16 und INT8. Jedes Cluster überträgt Daten mit 512 GByte/s an seine Nachbarn – im gesamten Chip laufen pro Sekunde 10 TByte an Daten.

Teslas D1-Chip (7 Bilder)

(Bild: Tesla)

Tesla setzt auf einen selbstentworfenen Befehlssatz, der zu 100 Prozent auf Machine Learning ausgerichtet sein soll – "kein unnötiges Silizium, kein Legacy-Support". D1 soll "Compute-Leistung auf GPU-Niveau, Flexibilität auf CPU-Niveau und I/O-Kapazitäten auf Niveau von Switches" bringen.

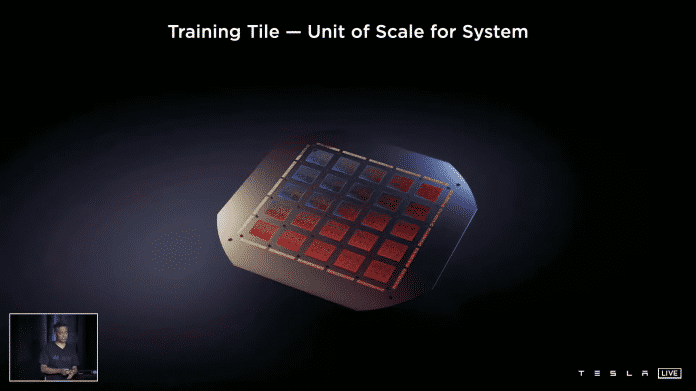

25 Chips auf einem Wafer

Bei der Integration geht es ans Eingemachte: 25 solcher D1-Prozessoren kommen auf einen fast kompletten Silizium-Wafer, über den die Kommunikation zwischen den Chips läuft – Training Tile genannt. Die Angaben sprechen für das InFO (Integrated Fan-Out) Wafer Level Packaging des Chipauftragsfertigers TSMC, womit auch dessen 7-nm-Prozess zum Einsatz kommen dürfte.

Jeder D1-Chip hat 576 SerDes, um mit Übertragungsraten von 8 TByte/s untereinander zu kommunizieren. Daten zwischen den Trainings Tiles werden mit 9 TByte/s in jede Richtung übertragen, also insgesamt 36 TByte/s. Der Anschluss an Hostsysteme erfolgt per PCI Express 4.0.

Teslas Training Tile (6 Bilder)

Wasserkühlung mit Bohrungen

Das Aufsetzen der Chips auf einem Wafer behebt Probleme, die Cerebras' Wafer Scale Engine 2 hat. Cerebras belichtet einen riesigen Prozessor auf einem einzelnen Wafer, muss aufgrund der üblichen Defektquote beim Belichten aber ordentlich Redundanz einbauen, zudem gestalten sich Kühlung, Stabilität und Stromversorgung aufwendig.

Tesla löst das vertikal: Im Wafer sind Bohrungen, um Wasserkühlungsrohre und Stromversorgungen durchzuführen. Selbstentworfene Spannungswandlermodule sitzen direkt über den Prozessoren, die 15 Kilowatt Strom kommen von unten, oben wird die Abwärme per Wasser abgeführt. Der Hersteller spricht vom "wahrscheinlich größten organischen Multi-Chip-Modul in der Industrie" (die Wafer Scale Engine 2 besteht technisch betrachtet nur aus einem riesigen Chip).

(Bild: Tesla)

Tesla will in einem künftigen Rechenzentrum 120 Training Tiles mit insgesamt 3000 D1-Prozessoren unterbringen, was eine BF16- beziehungsweise CFP8-Rechenleistung von 1,1 ExaFlops ergibt. Auf dem Papier ist das etwas weniger als das derzeitige Tesla-Rechenzentrum mit Nvidias A100-Karten, aufgrund der Spezialisierung will man neuronale Netze so trotzdem schneller trainieren. Tesla nutzt die Ergebnisse etwa für den eigenen Fahrassistenten. Erste Training Tiles laufen derzeit mit Taktfrequenzen von 2,0 GHz im Labor.

[Update, 20.08.21, 15:15 Uhr:] Korrektur: Ein D1-Chip erreicht eine BF16-Rechenleistung von 362 TeraFlops. Die zuvor angegebenen 1024 GigaFlops bezogen sich auf ein CPU-Cluster innerhalb des D1-Prozessors.

(mma)