AMD kündigt Prozessoren mit "aufgestapeltem" Cache-Chip an

Ab Ende 2021 will AMD einige Prozessortypen mit besonders großen L3-Caches namens "3D V-Cache" fertigen lassen, der 15 Prozent mehr Performance verspricht.

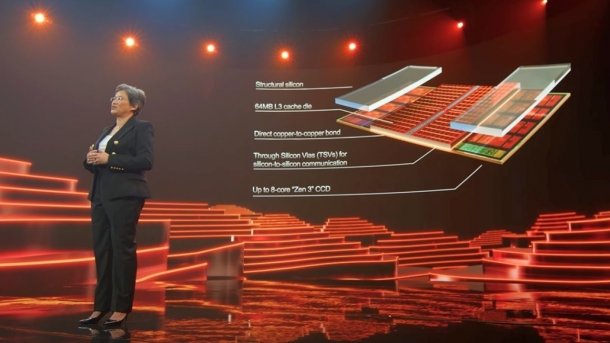

AMD 3D V-Cache Technology

(Bild: AMD/YouTube)

AMD-CEO Dr. Lisa Su kündigte in ihrer Keynote-Präsentation auf der virtuellen Messe Computex eine Innovation der Chip-Gehäusetechnik an: 3D V-Cache. Schon bisher lässt AMD die Epyc-Prozessoren für Server und die Ryzen-Prozessoren für Desktop-PCs aus mehreren Chiplets zusammensetzen. Diese sitzen jeweils nebeneinander auf einem gemeinsamen Die Carrier.

Künftig will AMD aber auch je zwei Dies stapeln lassen, also die Vertikale als dritte Dimension erschließen: Auf jedes Core Complex Die (CCD) setzt der Auftragsfertiger TSMC dabei ein zusätzliches SRAM-Die mit 36 Quadratmillimetern Fläche. Es erweitert den internen, 32 MByte großen L3-Cache des CCD um 64 MByte auf insgesamt 96 MByte.

(Bild: AMD)

Lisa Su zeigte das Muster eines Prototypen eines Ryzen 9 5900X mit 3D V-Cache, bei dem sowohl das Wärmeverteilblech (Integrated Heat Spreader, IHS) als auch zusätzliche Siliziumplättchen vom linken der beiden CCDs entfernt waren. Dadurch ist das quadratische SRAM-Die mit 6 mm Kantenlänge sichtbar.

Su betonte, dass man beim fertigen Serienprodukt das aufgestapelte SRAM-Die nicht mit bloßem Auge erkennt, weil rechts und links daneben passende Siliziumplättchen aufgebracht sind: Diese dienen der mechanischen Festigkeit und sorgen für Wärmeleitung vom unteren CCD zum IHS.

Der fertige Prozessor muss zudem dieselbe Höhe haben wie die Versionen ohne 3D V-Cache, damit der Anpressdruck des Kühlers passt. Daher werden die gestapelten Chiplets entsprechend gedünnt.

192 MByte L3-Cache

Der bisher noch hypothetische Ryzen 9 5900X mit zwei Achtkern-CCDs (mit je sechs aktiven Kernen), die je 32 MByte L3-Cache enthalten, kommt mit zwei zusätzlichen 64-MByte-SRAMs auf insgesamt 192 MByte L3-Cache. Im Vergleich zur bisherigen Version des Ryzen 9 5900X mit "nur" 64 MByte L3-Cache soll der Riesen-Cache im Schnitt 15 Prozent höhere Bildwiederholraten bei PC-Spielen mit Full-HD-Auflösung bringen.

Videos by heise

Auf andere CPU-Versionen mit 3D V-Cache ging Lisa Su nicht ein. In den vergangenen Monaten gab es aber Spekulationen um einen Serverprozessor mit dem angeblichen Codenamen "Milan-X" (der Epyc 7003 heißt "Milan"), der zusätzliche HBM2-Speicherchips haben soll. Für 2022 plant Konkurrent Intel mehrere Prozessoren mit der hauseigenen Foveros-Stapeltechnik.

Ohne Lot gestapelt

Die AMD-Chefin betonte, dass die Stapeltechnik von TSMC extrem hohe Kontaktdichten ermöglicht und keine Lötverbindungen nutzt. Stattdessen sitzen die Chips mit direkten Kupferverbindungen unmittelbar aufeinander. Außerdem kommen Through-Silicon Vias (TSVs) zum Einsatz, also vertikale Verbindungen durch ein Die hindurch.

[Update, 08.06.21, 12:15 Uhr:] In einer früheren Fassung schrieben wir, dass AMD und TSMC zwischen den gestapelten Chips sogenannte Micro-Bumps verwenden. Tatsächlich setzt der Chipfertiger beide Bausteine ohne solche Bumps direkt aufeinander. Wir haben die Meldung entsprechend angepasst. (ciw)