IBM POWER10 für Server mit über 960 Threads und Cluster mit 2 PByte RAM Update

Auf der Hot-Chips-Konferenz HC32 kündigt IBM den Serverprozessor POWER10 mit 7-Nanometer-Strukturen für das zweite Halbjahr 2021 an.

Für IBM Power Systems und für Supercomputer kommt in der zweiten Hälfte kommenden Jahres der Serverprozessor POWER10 (Power10), der den seit 2017 ausgelieferten Power9 ablöst

Der Power10 aus der 7-Nanometer-Fertigung von Samsung soll die Kapazität und Energieeffizienz damit bestücker Server um den Faktor 3 im Vergleich zu Power9-Maschinen [1] steigern. Bei KI-Algorithmen verspricht IBM Steigerungsmöglichkeiten bis zum Faktor 20 unter anderem dank neuer Datenformate wie BFloat16 (BF16).

Die neue Power ISA v3.1 des Power10, die IBM im Rahmen von OpenPOWER offenlegt, bringt über 200 neue Befehle. IBM hat zudem die externen Schnittstellen PowerAXON 2.0 und Open Memory Interface (OMI) auf bis zu 1 TByte/s beschleunigt (je 16 x8-Ports) und integriert PCI Express 5.0 (PCIe 5.0). Die PowerAXON-2.0-Schnittstelle erlaubt wie beim Power9 die kohärente Anbindung von Rechenbeschleunigern (CAPI). Ob der Power10 außer PCIe 5.0 auch CXL [2] beherrscht, blieb offen.

(Bild: IBM)

Schließlich gibt es neue Funktionen wie transparente RAM-Verschlüsselung (Transparent Memory Encryption, TME) zum Schutz von Daten in nichtflüchtigen Speichermodulen (Storage-Class Memory, SCM) sowie zur Abschottung von logischen Partitionen (LPAR) und Containern.

Bis zu 2 Petabyte Arbeitsspeicher

Pro Prozessorfassung (Socket) lassen sich bis zu 4 TByte RAM anbinden – das können aber auch andere Serverprozessoren wie AMD Epyc und Marvell ThunderX3. Doch weil OMI [3] unabhängig von der DDR-SDRAM-Generation arbeitet, lassen sich später auch mit DDR5-Speicher [4] bestückte OMI-DIMMs einsetzen und auch deren höhere Datentransferrate nutzen.

(Bild: Smart Modular)

Neu ist laut IBM die Funktion "Memory Inception", mit der ein Power10-Server via PowerAXON-Verbindung auf RAM zugreifen kann, das in einem anderen Power10-Server steckt. Das funktioniert nicht wie bei Remote DMA (RDMA) etwa via Infiniband, sondern der Speicher ist ebenso nutzbar, als wäre er physisch präsent. Memory Inception ermöglicht dadurch Server mit bis zu 2 Petabyte durchgehend adressierbarem RAM sowie flexibel konfigurierbare, "disaggregierte" Cloud-Racks, bei denen sich der RAM-Ausbau der Maschinen verändern lässt.

Bis zu 60 Kerne pro Fassung

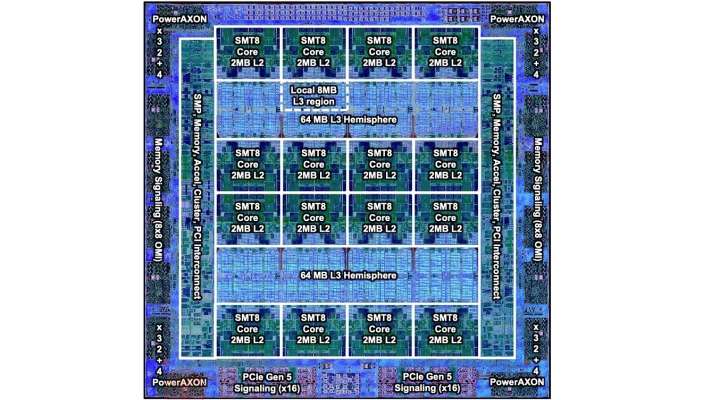

Auch die Konfiguration der Prozessoren ist sehr flexibel. In die Fassung (Socket) passen Module mit einem (Single Chip Module, SCM) oder mit zwei Dies (Dual Chip Module, DCM). Jedes Die kann bis zu 15 Kerne mit Achtfach-Multithreading haben (SMT8) oder 30 SMT4-Kerne. Somit sind bis zu 60 Kerne und 240 Threads in einem DCM möglich. Vier davon lassen sich per PowerAXON zu einer 4-Socket-Maschine mit 240 Kernen und 960 Threads verschalten.

(Bild: IBM)

Kommen SCM-Prozessoren zum Einsatz, lassen sich bis zu 16 Sockets direkt verschalten.

[Update:] Damit sind dann sogar bis zu 1920 Threads pro Server möglich.

PowerAXON 2.0 lässt sich aber auch zur Kopplung von Servern zu einem Cluster nutzen, etwa anstelle von Infiniband. IBM weist darauf hin, dass noch nicht veröffentlicht wird, welche Konfigurationen tatsächlich angeboten werden – man beschreibt nur die technischen Möglichkeiten.

Physisch sind beim 15-Kern-Die mit 18 Milliarden Transistoren auf 602 Quadratmillimetern Fläche 16 Kerne vorhanden. Um die Ausbeute (Yield) zu verbessern, nutzt IBM höchstens 15.

(ciw [6])

URL dieses Artikels:

https://www.heise.de/-4871443

Links in diesem Artikel:

[1] https://www.heise.de/news/IBM-POWER9-Server-zu-Weihnachten-3910888.html

[2] https://www.heise.de/news/Beschleuniger-Schnittstelle-CXL-AMD-ARM-IBM-Nvidia-und-Xilinx-im-Boot-4533253.html

[3] https://www.heise.de/news/Prozessoren-IBMs-Power-ISA-wird-ein-Open-Model-4502382.html

[4] https://www.heise.de/news/DDR5-RAM-Spezifikation-fuer-verdoppelte-Uebertragungsraten-finalisiert-4844322.html

[5] https://www.heise.de/ct

[6] mailto:ciw@ct.de

Copyright © 2020 Heise Medien