Intel AMX: Erste Informationen zur Advanced Matrix Extensions Architecture

Intels Advanced Matrix Extensions der Sapphire-Rapids-Xeons verknüpfen Rechenbeschleuniger über kohärente Interfaces.

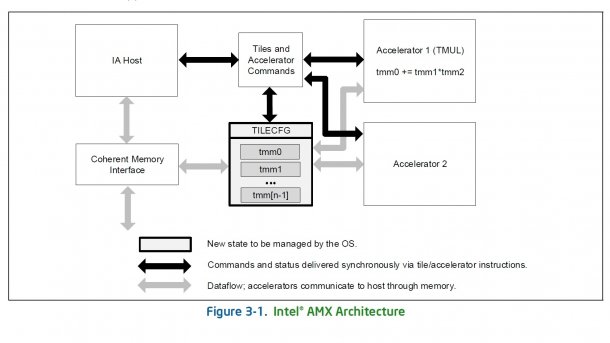

Intel Advanced Matrix Extensions Architecture (Intel AMX Architecture)

(Bild: Intel)

Intels für 2021 geplante 10-Nanometer-Serverprozessoren Xeon "Sapphire Rapids" bringen mit PCI Express 5.0 und dem Cache-kohärenten Compute Express Link (CXL) neue Möglichkeiten zur Einbindung von Rechenbeschleunigern. Mit der ebenfalls neuen Advanced Matrix Extensions Architecture (Intel AMX Architecture) dirigieren Programmierer das Zusammenspiel dieser Beschleuniger. Nun veröffentlicht Intel erste Informationen zu AMX.

(Bild: Intel)

Die Xeon-SP-Generation Sapphire Rapids hat für Intel besondere Bedeutung, weil sie unter anderem für den 500 Millionen US-Dollar teuren Autora-Supercomputer mit mindestens 1 Exaflops vorgesehen ist. Den größten Teil der Rechenleistung sollen darin wiederum "Ponte Vecchio"-Beschleuniger mit Intels GPU-Architektur Xe (Intel-Schreibweise Xe) liefern. Sie sind via CXL mit den Xeons gekoppelt. Vermutlich kommt als Hauptspeicher DDR5-SDRAM zum Einsatz.

AMX arbeitet mit Kacheln (Tiles)

Laut der "Intel Architecture Instruction Set Extensions and Future Features Programming Reference" sieht die AMX-Architektur einen Satz zweidimensionaler Kacheln (Tiles) vor, die Sub-Arrays größerer zweidimensionaler Arbeitsspeicherbereiche beschreiben sowie Beschleuniger, die auf diesen Tiles arbeiten.

Videos by heise

Als Software-Unterstützung stellt Intel Patches zur Erkennung von AMX durch GNU C bereit. Die ersten AMX-Patches für glibc erschließen AMX-BF16 (BFloat16), AMX-INT8 (8-Bit-Integer) und AMX-Tile.

Zur Programmierung künftiger High-Performance-Computing-(HPC-)Anwendungen entwickelt Intel zudem die einheitliche Schnittstelle oneAPI, für HPC etwa eine oneAPI-Anbindung von Data Parallel C++ (DPC++).

(ciw)