Intel Skylake-SP: Mesh statt Ringbus

Ab Skylake SP werden Kerne, L3-Cache, Speicher- und I/O-Kontroller über ein Netz (Mesh) verknüpft. Das soll nicht nur energieeffizienter sein.

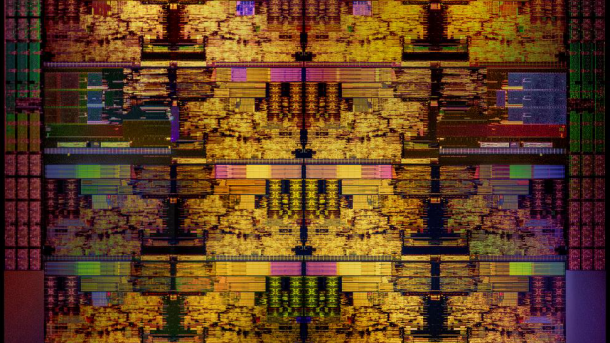

Mit 28 Kernen und zwei Speicherknoten -- den Skylake SP hat Intel auf dem Manufactoring Day veröffentlicht.

(Bild: Intel)

Intel ändert mit der für Sommer geplanten "Xeon Scalable Processor Family" (Skylake SP) die Technik der On-Chip-Kommunikation. Wie die Prozessorfirma auf einem Server-Workshop in Hillsboro bekannt gab, soll nicht mehr ein Ringbus-System, sondern ein Mesh für die Kommunikation zwischen Kernen, der Cache-Hierarchie, Speicher- und I/O-Controller Zuständig sein. Es soll bei größeren Kernzahlen besser skalieren, höhere Bandbreiten und niedrigere Latenzen ermöglichen und zudem auch energieeffizienter sein. Diese Mesh-Technik konnte Intel beim Xeon Phi schon bis hin zu 72 Kernen erproben.

(Bild: Intel)

Wie das vereinfachte, zur Veröffentlichung freigegebene Blockdiagramm zeigt, sind auch zwei Speicherknoten im Mesh integriert, das erklärt die beiden "Spezialkerne", die schon vorab auf den Die-Bildern vom Core X und Skylake SP zu sehen waren. Wieviele Speichercontroller jeder dieser Knoten beim Xeon enthält, hat Intel zwar noch nicht offiziell bekannt gegeben, das kann man aber den Die-Bildern entnehmen, außerdem funken es alle Spatzen schon lange im Internet von den Dächern. Der Core X im kleineren LGA2066-Sockel kann indes nur zwei Kanäle pro Speicherknoten betreiben.

Mit dem vor sechs Jahren herausgekommenen Sandy Bridge (4 bis 8 Kerne) begann Intel, einen Ringbus zur On-Chip-Kommunikation einzuführen. Mit Ivy-Bridge (4 bis 15 Kerne) wurde das Konzept beim größeren Xeon auf zwei Bussysteme erweitert, die über einen dritten Ringbus verbunden sind. Haswell- (4 bis 18 Kerne) und Broadwell-Xeon (4 bis 24 Kerne) verwenden zwei Ringbus-Systeme, die über zwei Brücken verbunden sind. Ab Skylake SP sind nun die Kerne horizontal und vertikal miteinander im Mesh vernetzt. Je weiter sie voneinander entfernt sind, um so mehr Schaltstationen (Hops) liegen dazwischen. Dabei kann die benötigte Zahl der Takte pro Hop horizontal und vertikal durchaus unterschiedlich sein. (as)