Retro Computing: 6502 mit 100 MHz

Ersatzteile für frühe Heimcomputer-Hardware werden langsam knapp: Fans zahlen inzwischen kleine Vermögen für alte Halbleiter. Zum Glück gibt es ja FPGAs.

- Carsten Meyer

Retro-CPUs als (fast) gattergenaue FPGA-Implementation sind keine ganz neue Idee: Schon die (inzwischen nicht mehr lieferbaren) GODIL-Module von Michael Randelzhofer konnten CPUs mit bis zu 48 Pins ersetzen, wenn man ihr FPGA (damals noch ein XC3S200) mit der Prozessor-Innenschaltung fütterte – zum Beispiel mit einem 6502-Kern, der selbst das alte Spartan-3-FPGA nur zu einem Bruchteil füllte.

Der Trend zum Retro-Computing hat die Ersatzteilversorgung nochmals verschlechtert, und viele Fans warten händeringend auf Lösungen. Neben den alten CPUs sind auch einige Peripheriebausteine betroffen, etwa I/O-Ports oder Spezialchips wie der Soundgenerator SID 6581.

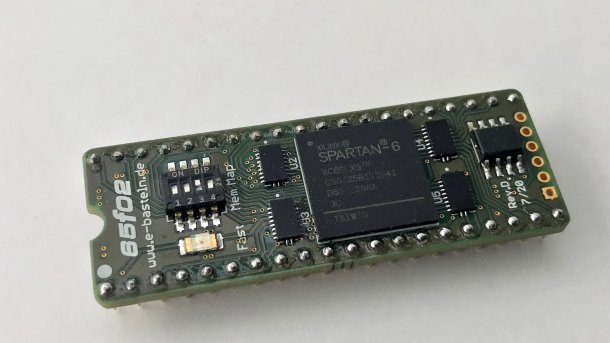

Trotz seines Namens könnte das schlanke Modul 65F02 von Jürgen Müller aus Hamburg durchaus auch andere CPUs emulieren, denn bei einem FPGA können die I/Os frei zugewiesen werden (Betriebsspannungsanschlüsse natürlich nicht). Seine 6502 auf einem XC6SLX9-FPGA von Xilinx läuft auch noch mit Taktfrequenzen von 100 MHz, während beim Original schon bei 1 oder 2 MHz Schluss war. Das Modul ist kaum größer als ein DIL40-Gehäuse.

System-on-FPGA

Besonderer Clou: Die 65F02 hat 64 kByte RAM an Bord (verwendet die im FPGA vorhandenen schnellen Block-RAMs). Sie kennt Memory Map des Host-Systems und lädt beim Hochfahren den kompletten RAM- und ROM-Inhalt des Hosts in den schnellen integrierten Speicher. Programme werden dann aus dem internen RAM mit vollen 100 MHz ausgeführt, ohne dass der Host auf diese Geschwindigkeit angepasst werden müsste. I/O-Zugriffe dagegen gehen auf den Adress- und Datenbus zum Host, und der wird natürlich mit dem Originaltakt des Hostsystems bedient.

Dazu kommen noch ein paar Tricks, um nach Möglichkeit auch zeitkritischen Code zur Steuerung der Peripherie (Delay-Schleifen und abgezählte Zyklen, wie z.B. im Apple II bei Paddle-, Lautsprecher und Floppy-Ansteuerung) automatisch im Originaltiming auszuführen. Man erhält also nur durch Austausch der CPU einen Rechner, der (im Falle der 1-MHz-Homecomputer) tatsächlich 100-mal so schnell ist, bei reinen I/O-Operationen dagegen nicht beschleunigt ist, so dass die Originalperipherie läuft.

Videos by heise

Die Design-Files einschließlich Verilog-Sourcen für das FPGA stellt Müller quelloffen zur Verfügung, das Platinenlayout wurde mit Autocad Eagle erstellt. Mit den Gerber-Files können Interessenten die Platine problemlos fertigen lassen. Die sollten sich dann aber auch die SMD-Bestückung zutrauen.

Ein weiterer sehr gesuchter Baustein ist der erwähnte Commodore-SID, für den als ausgelötetes Originalteil oft schon 80 Euro und mehr aufgerufen werden. Das ärgerte den Stuttgarter Andreas Beermann so sehr, dass er mit dem FPGASID-Projekt etwas Ähnliches für diesen nicht minder komplexen Soundgenerator-Baustein ins Leben rief. Der im Commodore C64 verbaute SID segnet öfter mal das Zeitliche, wenn man seine Portleitungen überlastet.

Beermanns FPGASID kann sogar zwei der 6581-SIDs oder der Nachfolger MOS8580 pin- und zyklenkompatibel emulieren und erlaubt zudem höhere Audio-Auflösungen als die Originale. Die FPGASID-Projektdateien stehen ebenso wie beim 65F02 zum Download zur Verfügung, man kann die kleine Platine aber auch fertig aufgebaut kaufen. Für knapp 80 Euro erhält man quasi zwei SIDs für bis zu 6-stimmige Melodien.

(cm)