OpenTitan: Google legt Sicherheitschip mit RISC-V-Technik offen

Googles "Titan"-Chips als Roots of Trust für Cloud-Server und Pixel-Smartphones bekommen einen offengelegten Nachfolger.

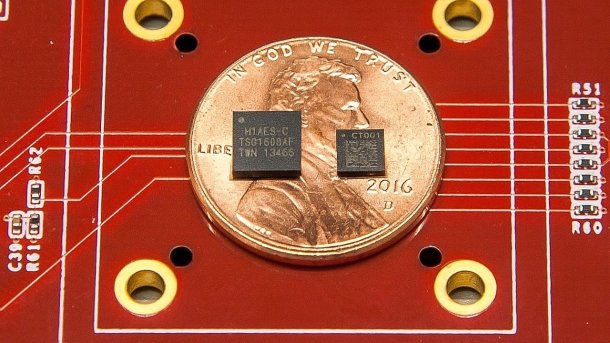

Google Titan (links) und Titan M

(Bild: Google)

Seit einigen Jahren nutzt Google die selbst entwickelten "Titan"-Chips als Hardware-Vertrauensanker (Root of Trust, RoT) in den hauseigenen Cloud-Servern, in Chromebooks und in den Smartphones Pixel 3 und 4. Zukünftige "OpenTitan"-Chips mit RISC-V-Mikrocontroller entwickelt Google nun in einer offenen Partnerschaft mit Organisationen und Firmen wie lowRISC, Western Digital (WD), Giesecke & Devrient (G&D), Nuvoton und der RISC-V-Arbeitsgruppe der ETH Zürich.

OpenTitan-Chips sollen zuerst in Googles Cloud-Servern zum Einsatz kommen. Cloud-Kunden von Google können das Design der OpenTitan-Chips selbst verifizieren; letztlich müssen sie nur noch dem Auftragsfertiger vertrauen, der die physischen Silizium-Dies produziert. Damit will Google das Vertrauen seiner Kunden stärken. Es ist ausdrücklich erwünscht, dass auch andere Firmen OpenTitan für eigene Zwecke anpassen und nutzen. WD etwa plant den Einsatz der Sicherheitschips in künftigen Speichersystemen.

Titan-Konkurrenz

(Bild: Google)

Laut Google gibt es auf dem Markt keine Sicherheitschips mit dem gewünschten Funktionsumfang. Titan hat mehrere externe Schnittstellen etwa für Flash-Speicherchips und die Firmware-Chips auf PCIe-Zusatzkarten. Darüber kann Titan beispielsweise die Integrität des Server-BIOS und der Firmware von Netzwerk- und RAID-Adapterkarten prüfen. Erkennt Titan eine Manipulation, stoppt er beispielsweise den Bootvorgang.

Auch Amazon (Nitro) und Microsoft (Cerberus) entwickeln eigene Chips als Cloud-Vertrauensanker. Einige Cerberus-Spezifikationen hat Microsoft im Rahmen des Open Compute Project (OCP) veröffentlicht. Außerdem hat Microsoft die "Pluto"-Engine für IoT-Prozessoren mit Azure-Sphere-Anbindung entwickelt. Mediatek integriert Pluto in den MT3620 mit ARM-Kernen und eingebautem WLAN-Controller.

Von solchen proprietären Chips soll sich OpenTitan durch das offene Design unterscheiden.

Mit der hochkarätig besetzten Sicherheitsabteilung Project Zero, die unter anderem an der Aufdeckung der CPU-Sicherheitslücken Spectre und Meltdown beteiligt war, bewirbt Google ebenfalls die eigene Kompetenz für Cybersicherheit. Bei Google ist aber auch das RISC-V-Mastermind David Patterson beschäftigt.

Titan-Funktionen

(Bild: Google/Hot Chips HC31)

Der 32-Bit-Mikrocontroller des OpenTitan verwendet den RISC-V-Kern Ibex (früher Zero-riscy), der vom Pulp-Team der ETH Zürich entwickelt wurde. Er erfüllt die RISC-V-Spezifikation RV32IMC.

Die bisherigen Titan-Chips für Cloud-Server, für Chromebooks (Titan H1) und Smartphones (Titan M) arbeiten mit ARM-Rechenkernen wie dem Cortex-M3 oder dem SecurCore SC300. In diesen Titans stecken Funktionen, die man aus TPMs und SmartCard-ICs anderer Hersteller kennt: Zufallszahlengenerator und Krypto-Funktionsblöcke für AES-Verschlüsselung und digitale Signaturen mit RSA oder elliptischen Kurven (EC).

Mehrere Speicherbereiche, die sich nicht über externe Schnittstellen auslesen lassen, sind gegen Hardware-Attacken geschützt. Solche Angriffe bestehen etwa darin, die Leistungsaufnahme des Chips zu analysieren, um daraus auf interne Geheimnisse zu schließen. Oder man schleift den Chip auf, um ihn unter dem Mikroskop mit Prüfspitzen oder Lichtimpulsen zu traktieren.

Titan-Chips speichern außer einer eindeutigen ID-Nummer einen intern generierten kryptografischen Schlüssel, der den Chip niemals verlässt. Den öffentlichen Hash liest der Hersteller nach der Fertigung aus, um ihn sicher extern zu speichern. Erst dann werden die Chips zum jeweiligen Mainboard-Hersteller versandt. Nur ein einziges Mal programmierbare Register - auch One Time Programmable (OTP) oder eFuse genannt - lassen sich dazu nutzen, vertrauenswürdig geprüfte Schritte der Hardware-Fertigung zu dokumentieren. Der Rollback-Schutz verhindert mithilfe von Zeitstempeln das Laden älterer oder als unsicher markierter Firmware-Versionen. (ciw)