I3C und xSPI

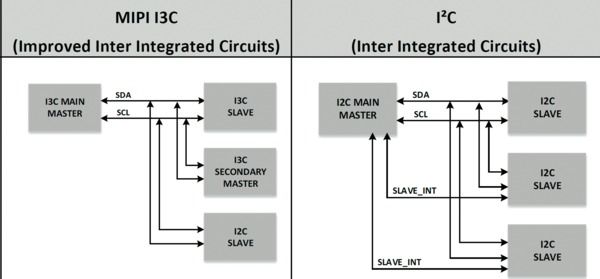

Die verbreitete Schnittstelle Inter-Integrated Circuit (I2C), die etwa auch als System Management Bus (SMBus) im PC dient, erhielt 2016 den schnelleren Nachfolger I3C von der Mobile Industry Processor Interface (MIPI) Alliance. I3C ist als abwärtskompatibler I2C-Nachfolger vor allem für leistungsfähige Sensoren gedacht. Außerdem überträgt I3C Interrupts ohne zusätzliche Leitungen als Nachricht im Protokoll. Mit 10,6 MBit/s übertrifft I3C I2C um mehr als das Dreifache, der Modus High Data Rate nutzt ternäres Encoding für 33 MBit/s. So kann I3C in manchen Fällen auch das leistungsfähigere Serial Peripheral Interface (SPI) ersetzen, welches doppelt so viele Signalleitungen benötigt, nämlich vier statt zwei.

Doch bei SPI gibt es ebenfalls eine Neuerung namens xSPI. SPI schafft bisher maximal 60 MBit/s, xSPI soll bis zu 400 MByte/s übertragen. SPI wird – auch in PCs – zur Anbindung des (NOR-)Flash-Speicherchips mit dem BIOS-Code genutzt. Zwecks schnellerer Verarbeitung kopiert das System beim Booten große Teile des Code ins RAM. Winzige, sparsame IoT-Geräte haben jedoch nur wenig RAM beziehungsweise SRAM, sie führen Code direkt aus dem NOR-Flash aus. Dabei hilft einerseits hohe Transferrate, andererseits soll xSPI auch niedrige Latenzen gewährleisten. Adesto liefert Muster des EcoXiP ATXP032 mit 4 MByte Flash und xSPI-Interface; XiP steht dabei für Execute-in-Place. (ciw@ct.de)