Der Euro-Prozessor

Die EU fördert die offene CPU-Architektur RISC-V

RISC-V statt Intel, ARM oder AMD: Neue Open-Source-Prozessoren haben viele Befürworter und gute Chancen, im Rahmen der European Processor Initiative sogar Supercomputer zu erobern. Viele RISC-V-Entwicklungen zielen bisher auf Systems-on-Chip für Embedded Systems.

Schon über 100 Firmen und Institutionen haben sich der erst 2015 gegründeten RISC-V Foundation angeschlossen, um neue Technik für Mikrocontroller und Systems-on-Chip (SoCs) zu entwickeln. Nvidia will RISC-V-Kerne in zukünftigen Grafikchips einbauen, WD plant gleich Milliardenstückzahlen, denn RISC-V soll in Controllern künftiger Festplatten und SSDs stecken. Auch Google, Tesla, Samsung, Qualcomm, IBM, Micron und NXP gehören dazu; sogar Intel hat Risikokapital in SiFive gesteckt, den Lieferanten der ersten RISC-V-Prozessoren.

Ein 64-Bit-Chip kommt gerade auf den Markt, auf den vier Kernen des SiFive Freedom Unleashed FU540 läuft Linux oder FreeBSD. Die Rechenleistung des FU540 unter Linux ähnelt der des Broadcom-Prozessors BCM2837 auf dem Raspberry Pi 3. Für die Zukunft sind RV128-Chips, Vektor- und DSP-Erweiterungen geplant, sie könnten dereinst einen europäischen Exaflops-Superrechner befeuern. Die European Processor Initiative (EPI) sieht RISC-V als einen heißen Kandidaten für einen europäischen Prozessor.

Auf dem Workshop der RISC-V Foundation Anfang Mai in Barcelona herrschten Aufbruchstimmung und gute Laune. Die Experten versammelten sich nur wenige Schritte entfernt vom „Mare Nostrum“-Supercomputer, wo Forscherteams unter anderem ARM-Prozessoren auf ihre Eignung fürs High-Performance Computing (HPC) abklopfen. Die EU will ihre Abhängigkeit von US-amerikanischer und chinesischer Technik reduzieren und nimmt viel Geld in die Hand, über mehrere Jahre verteilt sollen rund 1 Milliarde Euro fließen. Ziel des European High-Performance Computing Joint Undertaking (EuroHPC JU) sind eigene Kernkomponenten für Supercomputer, die Mitte der 2020er-Jahre Rechenleistung im Exaflops-Bereich liefern können.

Dabei spielt der Brexit-Ausstieg eine Rolle: Großbritannien verlässt bald die EU, steckt jedoch große Summen in Superrechner. Das hat auch damit zu tun, dass Großbritannien als Atommacht Rechenleistung für die Waffenforschung braucht. Unter anderem deshalb liefern sich die USA ein HPC-Wettrüsten gegen China und betreiben Supercomputer in Nationallabors wie Los Alamos, Oak Ridge und Sandia. Auch mehrere Forscher, die Vorträge auf dem RISC-V Workshop hielten, arbeiten mit Zuschüssen der US-Rüstungsforschungsagentur DARPA.

Offenes Rennen

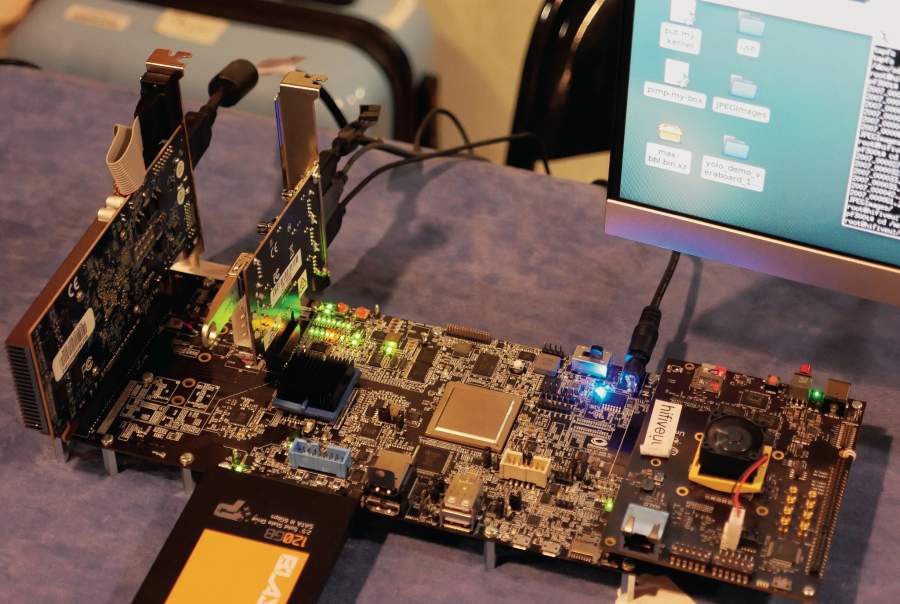

Bisher sind RISC-V-Prozessoren noch weit von Superleistung entfernt. Doch stolz präsentierte Palmer Dabbelt von SiFive das Entwicklersystem HiFive Unleashed mit FU540, laufend unter Fedora. Sogar der Browser samt JavaScript und Videowiedergabe funktionierte. Das leider rund 1000 US-Dollar teure Board war dabei freilich mit dem nochmals doppelt so teuren FPGA-Erweiterungsboard des SiFive-Kooperationspartner Microsemi gekoppelt. Das FPGA dient dabei quasi als Chipsatz, um eine AMD-Radeon-Grafikkarte, eine SATA-SSD sowie einen USB-Hostadapter anzuschließen.

SiFive plant deutlich billigere Entwicklerboards; auf der Hand liegt eine Variante, die RISC-V-CPU und FPGA-„Chipsatz“ kombiniert. Zum vollständig offenen Prozessor ist es aber noch ein weiter Weg, wie SiFive einräumt: Im FU540 steckt auch proprietäres geistiges Eigentum (Intellectual Property, IP). Dazu gehören beispielsweise Taktgeber (PLLs), ROM-Speicherzellen, das Interface zum DDR4-SDRAM sowie der Gigabit-Ethernet-Controller.

Die sparsame RV32I-Variante von RISC-V ist schon weiter: Sie ist als flexibel erweiterbarer, potenziell extrem sparsamer Mikrocontroller für Systems-on-Chip (SoCs) gedacht. Der Arduino-kompatible HighFive1 kostet 60 Euro und soll die Eignung von RISC-V für Sensoren oder für vernetzte IoT-Geräte zeigen. Auch Security-Experten sind an der offengelegten RISC-V-Mikroarchitektur interessiert: Potenziell lassen sich sichere, formal verifizierte Controller ohne Hintertüren entwickeln. Der offene Mikrokernel seL4 mit beweisbar korrekter Implementierung wird für RISC-V portiert. So mancher Chipkarten-Experte war auf dem RISC-V-Workshop zu sehen, aber auch Zulieferer für die Rüstungsindustrie oder Entwickler von Blockchain-Anwendungen wie Kryptowährungen.

Die RISC-V-Erfinder, darunter CPU-Altmeister David A. Patterson – er signierte in Barcelona Bücher und arbeitet mittlerweile auch für Google –, haben das Konzept geschickt festgelegt: Die Binärschnittstelle (Application Binary Interface, ABI) der RISC-V Instruction Set Architecture (ISA) soll nachträglich nicht verändert werden. Das erleichtert es, für RISC-V zu programmieren. Trotzdem ist die Mikroarchitektur flexibel, aber über optionale Erweiterungen. Diese Ideen treffen offenbar einen Nerv: Firmen wie NXP erklären, dass sie bei der Entwicklung neuer Systems-on-Chip mittlerweile länger an der Software als an der Hardware arbeiten.

Rasanter Fortschritt

Viele Universitäten und Forschungsinstitute beschäftigen sich weltweit mit RISC-V, unter anderem als Experimentierfeld zur Untersuchung von Sicherheitsrisiken. Die Seitenkanalangriffe Meltdown und Spectre spielten in mehreren Vorträgen auf dem Workshop eine Rolle. Die ETH Zürich und die Uni Bologna entwickeln hingegen konkrete Chips, von denen die ersten schon als Muster gefertigt wurden. Ein Team kümmert sich um die besonders effiziente PULP-Plattform, etwa für IoT-Sensor-SoCs mit dem Ri5CY-Kern (gesprochen Riski). Florian Zaruba von der ETH stellte seine Arbeit am 64-Bitter Ariane vor, den Globalfoundries auf Silicon-on-Insulator-Wafern mit der Fertigungstechnik 22FDX produziert. Für den Basisentwurf des In-Order-Kerns vom Typ RV64IMC mit sechsstufiger Pipeline hat das Team lediglich vier Monate gebraucht.

Zu den Berühmtheiten der Szene gehört Transmeta-Gründer Dave Ditzel, der nach einigen Intel-Jahren nun die Firma Esperanto Technologies (ET) aus der Taufe gehoben hat. Zwei Entwicklungsziele sind bekannt: ein Chip mit über 4000 Kernen vom Typ ET-Minion mit Tensor-Erweiterungen für KI-Anwendungen sowie ET-Maxion-Prozessoren mit besonders hoher Singlethreading-Rechenleistung. Letzteren soll TSMC mit 7-nm-Technik fertigen.

Euro-Prozessor

Ein Verbund aus 23 europäischen Firmen unter der Leitung des großen französischen IT-Dienstleisters Atos will nun als European Processor Initiative (EPI) eine „EU-CPU“ für Supercomputer, KI und autonomes Fahren entwickeln. Zu den Beteiligten gehören der Autohersteller BMW, Infineon und STMicroelectronics, aber etwa auch die ETH Zürich und das Barcelona Supercomputing Center (BSC). Im erwähnten Mare Nostrum rechnen unter anderem ARM64-Kerne in Maschinen der Atos-Sparte Bull.

Das BSC koordiniert in der EPI die Entwicklung eines RISC-V-Rechenbeschleunigers. Im Gespräch mit c’t erklärte Mateo Valero, Gründer und Direktor des BSC, dass der RISC-V-Beschleuniger mit einem Allzweckprozessor kooperieren soll, dessen Mikroarchitektur noch offen ist; ein wahrscheinlicher Kandidat ist ARMv8 mit Scalable Vector Extensions (ARM SVE). Diese Technik entwickelt derzeit Fujitsu für einen Nachfolger des K Computer am japanischen Forschungsinstitut Riken.

Laut Valero könnte RISC-V zwar irgendwann schnell genug werden für einen HPC-Allzweckprozessor. Doch das passt nicht in den aktuellen EPI-Zeitplan. Ob OpenPOWER eine Alternative zu ARM SVE für den EPI-Allzweckprozessor ist, dazu will sich derzeit auch der EPI-Chef Philippe Notton von Atos nicht äußern.

Western Digital schickte seinen Chief Technology Officer (CTO) Martin Fink zum RISC-V Workshop, um die großen RISC-V-Pläne von WD vorzustellen – ohne allzu konkret zu werden. Jedenfalls soll RISC-V vom simplen SSD-Controller mit eingebauter Verschlüsselung bis hin zum High-End-Speichersystem mit Gen-Z-Interface zum Einsatz kommen. WD sieht Profitchancen schwinden, weil Software-defined Storage auf Basis billiger Standardkomponenten in immer lukrativere Märkte vordringt – künftig etwa mit Intels 3D XPoint. Martin Fink war bis Ende 2016 CTO der HPE-Forschungssparte HP Labs und hatte dort seit 2006 die neuartige Plattform „The Machine“ entwickelt, um die Vorzüge des „speichergetriebenen Rechnens“ (Memory-driven Computing) zu demonstrieren.

Auch der Speicherchiphersteller Micron engagiert sich bei RISC-V. Bestimmte Algorithmen, etwa zum Sortieren von Daten, ließen sich demnach wesentlich effizienter von intelligenten DRAM-Chips als von Prozessoren erledigen, die sämtliche Daten vor dem Durchsuchen erst blockweise laden müssen. Verwandte Ideen zu Processing in Memory (PIM) geistern allerdings schon seit Jahrzehnten durch die IT-Landschaft: Computational RAM, Micron Automata. Auch das zeigt, wie weit das Feld der RISC-V-Technik ist. Die Entwicklergemeinde gibt sich enthusiastisch – bleibt zu hoffen, dass bald praktisch nutzbare RISC-V-Systeme auf den Markt kommen. (ciw@ct.de)