Hot Chips: Details zu Intels Supercomputer-Beschleuniger Xeon Phi Knights Landing

Intel nutzt nicht das hauseigene IDF, sondern die Hot-Chips-Konferenz in Cupertino, um ewas mehr Licht auf das Innenleben und die Performance des fürs Jahresende geplanten Xeon Phi x200 Knights Landing zu werfen

Die Konferenz Hot Chips lässt in die Zukunft der Prozessoren blicken - und in diesem Jahr auch in die Vorhaben Intels für das Supercomputing. Der Supercomputer-Beschleuniger Xeon Phi Knights Landing steht an, und Intel gibt einige weitere Details des seit langem in Entwicklung befindlichen Prozessors bekannt.

Mit Feinheiten zum neuen Interconnect Omnipath, einem Interconnect zur Verbindung der Knoten in Supercomputing-Systemen, will Intel aber noch bis zur Hot Interconnect am 26. August warten. Die 72 Kerne sind in Kacheln (Tiles) zu zweit organisiert, die dann in einem 2D-Mesh zusammen mit den Speicher-Controllern, dem PCIe-3.4-Interface und dem DMI-Controller kommunizieren. Neben den beiden DDR4-Controllern gibt es acht Interfaces zu den auf dem Gehäuse untergebrachten schnellen Hybrid Cubes von Micron. Dieser High-Bandwidth-Speicher kann in drei Modi arbeiten, die beim Booten festgelegt werden: als transparenter Cache, als Speicher mit eigenem Adressbereich oder hybrid mit 25 oder 50 % Cache.

Als Speicher wird er über einen eigenen Numa-Knoten angesprochen. Mit speziellen Befehlen kann der Programmierer ihn allozieren.

Der Omni-Path-Controller der vorgesehenen speziellen Fabric-Version wird mit im Gehäuse untergebracht. Er belegt dann 32 der vorhandenen 36 PCIe-Lanes.

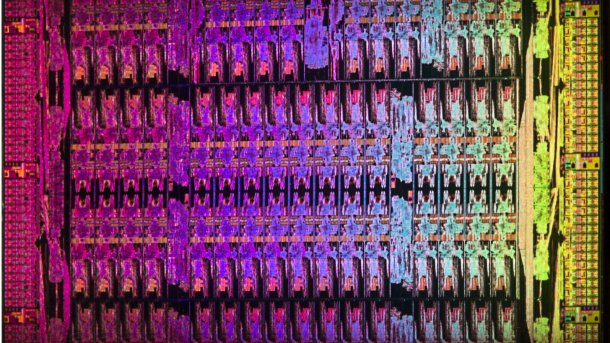

(Bild: Intel)

Die Silvermont-Kerne wurden für den HPC-Einsatz erheblich modifiziert: Vierfach Hyper-Threading, tieferes Out-Of-Order, Höhere Bandbreiten, größere TLBs – und dann kommen die beiden VPUs mit AVX512 hinzu. Die L1-Cache sind wie beim Silvermont 32 KByte groß. Die beiden Kerne einer Kachel teilen sich einen 16-fach assoziativen L2-Cache von 1 MByte, der auch für die Cache-Konsistenz zwischen den Kacheln sorgt. Das Mesh kann dabei unterschiedlich konfiguriert werden: Jeder mit jedem, in Quadranten aufgeteilt oder als sogenanntes Sub-NUMA-Clustering.

Xeon Phi Knights Landing - Benchmarks

Interessant sind auch die ersten Performance-Angaben, wiewohl Intel sie nur in sehr groben Balken preisgibt. Danach erreicht der Xeon Phi x200 etwa 60 Prozent eines Xeon-E5-2697v3-Systems bei SPECint_base2006_rate und 87 Prozent bei SPECfp_base2006_rate, mithin also etwa 720 und 750.

Bei SPECint liegt er damit nur knapp vor dem Mars-Prozessor mit 64 ARMv8-Kernen von Phytium. Bei SPECfp ist er etwa 30 Prozent schneller. In der Energiebilanz schlägt er mit 200 Watt TDP zu Buche, Mars aber nur mit 120 Watt, während die beiden Xeon-E5-Prozessoren 290 Watt TDP aufweisen.

(Bild: Intel)

(as)