Sparsamer 1000-Kern-Prozessor

Forscher der Uni Kalifornien haben einen Chip entwickelt, der 1000 winzige 16-Bit-Rechenkerne vereint, die sich unabhängig voneinander programmieren lassen.

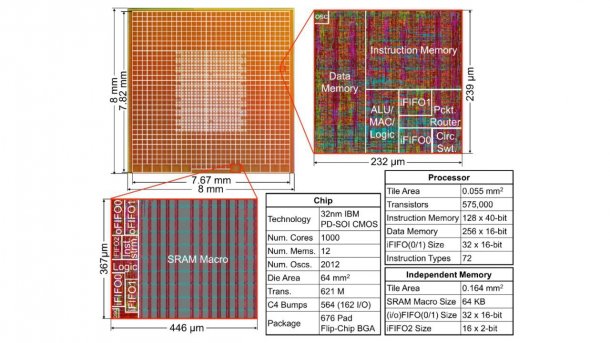

KiloCore-Chip der University of California, Davis

(Bild: University of California, Davis)

Schon seit Jahren arbeitet Professor Bevan Baas von der University of California at Davis an Vielkern-Prozessoren; 2006 hatte er den 36-kernigen AsAP vorgestellt, später den AsAP 2 mit 167 Kernen. Nun hat ein Team seines VLSI Computation Lab den KiloCore vorgestellt: Einen Chip mit 1000 unabhängig voneinander programmierbaren Rechenkernen. Es geht also um Multiple Instructions, Multiple Data (MIMD).

Der KiloCore ist nicht nur der Chip mit den meisten Rechenkernen, sondern auch der Chip mit der höchsten CPU-Taktfrequenz, der je von einer Universität entwickelt wurde: Bis zu 1,87 GHz schaffen die Kerne, stabil liefen sie bei 1,78 GHz. Dann schaffen alle Rechenwerke zusammen 1,78 Billionen Operationen pro Sekunde. Dabei geht es aber nicht um aufwendige Gleitkomma-Operationen, also Flops, sondern einfachere Instruktionen, von denen der KiloCore 72 verschiedene beherrscht.

Sparsam und effizient

(Bild: University of California, Davis)

Bei geringer Taktfrequenz ist der KiloCore dank niedriger Betriebsspannung sehr effizient: Bei 115 MHz verarbeitet er 115 Milliarden Operationen pro Sekunde und nimmt dann nur 1,3 Watt Leistung auf. Für 1 GHz braucht er 0,84 Volt und benötigt dann schon 13,1 Watt, wie das auf dem 2016 Symposium on VLSI Technology and Circuits präsentierte Paper erklärt.

Den Chip fertigt "IBM" – eher wohl Globalfoundries – mit 32-nm-Strukturen in PD-SOI-Technik. Zwei On-Chip-Netzwerke verbinden die 1000 Kerne mit 12 unabhängigen Speicherblöcken, die jeweils 64 KByte SRAM umfassen. In jedem Kern steckt eine separate Router-Schaltung mit eigenem Takt. Insgesamt besitzt der Chip 2012 Oszillatoren (1000 Kerne mit 1000 Routern plus 12 SRAM-Blöcke), die unabhängig voneinander laufen, ihre Frequenzen wechseln können und in sehr kurzer Zeit stoppen und wiederanlaufen, um Energie zu sparen.

Ebenfalls um Energie zu sparen, verzichtet der KiloCore auf explizite Caches. Es gibt in jedem Kern 128 × 40 Bit Instruktionsspeicher, 256 × 16 Bit Datenspeicher und zwölfmal die erwähnten 64 KByte SRAM.

(Bild: University of California, Davis)

Unterschiedliche Kern-Gruppen des KiloCore können unabhängig voneinander Rechenaufgaben gleichzeitig erledigen; in ihrem Paper erwähnen die Forscher beispielsweise WLAN-Berechnungen, FFT und AES parallel.

Die Arbeit am KiloCore-Chip der Uni Kalifornien wurde vom US-Verteidigungsministerium gefördert. Bereits 2006 hatte die später übernommenen Firma Rapport einen KiloCore-Chip vorgeschlagen, die einen 256-Kern-Chip unter anderem für die Verarbeitung von Videodaten demonstriert hatte. (ciw)