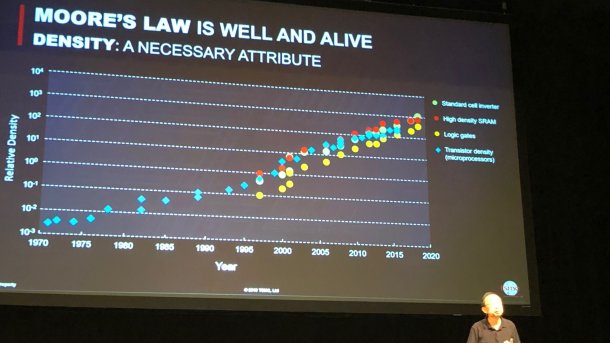

Chip-Auftragsfertiger TSMC: Moore's Law lebt!

Der Auftragsfertiger TSMC hat auf der Hot Chips einen Ausblick gegeben, was von den nächsten Fertigungsstufen zu erwarten ist.

(Bild: c't / Florian Müssig)

TSMCs Forschungschef Philip Wong eröffnete seine Keynote auf der Hot Chips mit einem eindeutigen Statement: Moore's Law lebt – es sei entgegen aller Unkenrufe sogar nicht einmal krank! Auf absehbare Zeit werde sich daran auch nichts ändern; Wong zufolge soll es auch noch im Jahr 2050 und darüber hinaus gelten. Die Metrik, die Wong für seine Aussage nutzt, ist die Packdichte der Transistoren.

In der Vergangenheit war die Strukturbreite die gängige Stellschraube für immer enger gepackte Transistoren, und daran werde sich in absehbarer Zeit auch nichts ändern. Die 7-nm-Fertigungsstraßen laufen in der Massenproduktion, 5-nm-Chips seien in geringen Stückzahlen verfügbar, und danach werde es sicherlich auch weitere, noch feinere Fertigungsprozesse geben.

(Bild: TSMC)

Wong erinnerte allerdings daran, dass die Transistoren und ihre Größen nicht die einzigen relevanten Faktoren seien. Zusätzlich kämen andere Verbesserungen hinzu, die ebenfalls helfen würden. Als Beispiele aus der jüngeren Vergangenheit nannte Wong SOI (Silicon on Insulator) und FinFETs, also dreidimensionale Strukturen auf dem Wafer. Die aktuellen Bemühungen, statt großer monolithischer Dice mehrere kleinere Chiplets zu einem großen Ganzen zusammenzuschalten, sieht Wong als einen weiteren Kniff unabhängig von einer konkreten Strukturbreite an.

(Bild: TSMC)

Er verwies in diesem Zusammenhang auf Gordon Moores anno 1965 erschienenen Veröffentlichung: Auf Seite 3 findet man dort die Bemerkung, dass es mitunter sinnvoll sein könne, große Systeme aus kleineren Funktionseinheiten zusammenzusetzen, die einzeln gefertigt und dann zusammengefügt werden. Abgesehen von der konkreten Bezeichnung Chiplet hatte Moore diese also bereit selbst vorausgesagt.

Speichermauer

Ein immer stärker in Erscheinung tretendes Phänomen ist die stetig anwachsende Datenmenge. So werden bei KI-Anwendungen abhängig vom gewählten neuronalen Netz mindestens 80 Prozent der verbratenen Energie aufgewendet, um die Daten an die eigentlichen Rechenwerke heran- und danach wieder wegzuführen.

CPU, GPUs und KI-Beschleuniger arbeiten dagegen an, indem immer größere Caches integriert werden. Für eine wissenschaftliche Veröffentlichung hat Wong den Anstieg extrapoliert: Bei einem fiktiven künftigen 1,4-nm-Prozess würde ein durchschnittlicher Chip bei einer linearen Entwicklung fast 4 GByte Cache enthalten.

3D-Packaging

(Bild: TSMC)

Zudem wird externer Speicher immer näher an die Chips herangeführt, weil so hohe Bandbreiten, geringe Latenzen und wenig Energieverbrauch locken. Bei GPUs und KI-Beschleunigern findet man HBM-Speicherstapel, die Teil des Package geworden sind; Smartphones-SoCs tragen ihre Speicherchips auf dem Rücken. Bei mehreren Chiplets und Ram-Chips muss man diese übereinander anbringen – nur so lassen sich hohe Bandbreiten zwischen den Komponenten erzielen.

Das Ausnutzen der dritten Dimension hilft ungemein, um die Packdichte immer weiter zu steigern. In Kombination mit Chiplets ergeben sich sogar neue Anwendungsmöglichkeiten, indem nichtflüchtiger Speicher nahe an die CPU rückt. Flash ist für diesen Einsatzzweck zu lahm; MRAM, Phase-Change-Memory und etliche andere Techniken seien vielversprechender aufgestellt.

Neue Materialien

(Bild: TSMC)

Abschließend wandte sich Wong auch noch neue Materialien zu. Die aktuellen Transistoren würden zwar noch ein bisschen halten, doch irgendwann ist Schluss: Wenn die Strukturgrößen in den Bereich weniger Atomlagen schrumpfen, verändern sich das Verhalten. Alternative Verbindungen wie MoS2, WSe2 oder WS2 zeigen hingegen auch bei Dicken von einem Nanometer und darunter noch gute Resultate. Auch an den schon länger bekannten Kohlenstoffnanoröhrchen wird weiterhin viel geforscht.

Womöglich wird ein Materialwechsel aber auch dadurch notwendig, dass sich sonst keine 3D-Chipstapel bauen lassen: Wenn eine Lage zur Verarbeitung hohe Temperaturen benötigt, diese aber darunterliegenden Ebenen schadet, dann hat man nichts gewonnen.

tl;dr

Kleinere Strukturbreiten sind laut TSMCs Forschungschef Philip Wong nur ein Baustein auf dem Weg zu immer leistungsfähigeren Computern. So eng wie möglich an die Logik angebundener Speicher und ein 3D-Verbund aus verschiedenen Chiplets sind mindestens genauso wichtig. (mue)