Kostenlose Custom-Chips von Google und Skywater

Eine Kooperation von Google und Skywater Technology Foundry soll Universitäten, Start-Ups und Hardcore-Makern selbst entworfene Chips ermöglichen.

- Carsten Meyer

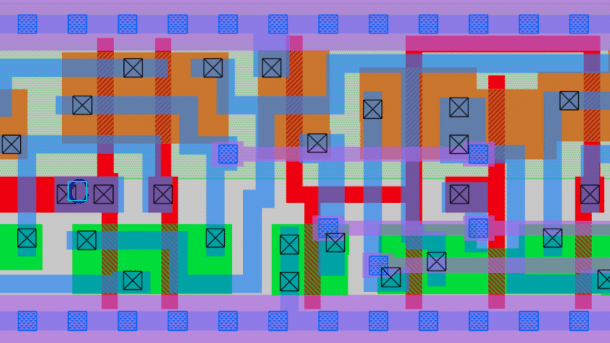

Bislang war der Entwurf und vor allem die Herstellung eigener Chip-Designs (ASICs) ein ziemlich teures Vergnügen, das sich nur größere Firmen leisten konnten. Dank einer Kooperation von Google und Skywater Technology Foundry soll die Fertigung von Custom-Chips bald kostenlos möglich sein – so lange man sich an gewisse Vorgaben hält: Das Design muss nach Apache-2.0-Lizenz quelloffen sein, die maximale Chipfläche der im 130-nm-Prozess gefertigten Halbleiter darf maximal 10 mm² betragen und die Stückzahl ist auf 100 Chips beschränkt.

Skywater stellt dafür ein Process Development Kit zur Verfügung, das sich momentan noch im Alpha-Stadium, einer "Experimental Preview", befindet. In einem Gespräch mit der Free and Open Source Silicon Foundation (FOSSi) kündigte Tim Ansell, langjähriger Open-Source-Spezialist bei Google, einen ersten Produktions-Testlauf für den November dieses Jahres an.

Im PDK sind Standard-Logikzellen enthalten, IPs (vorgefertigte Designstrukturen) für Hochfrequenz- und RAM/Flash-Blöcke sollen folgen. Wie bei FPGAs erfolgt das Design in den Hardware-Beschreibungssprachen VHDL oder Verilog, Erfahrungen auf diesem Gebiet sind beim Design also Voraussetzung.

Empfohlener redaktioneller Inhalt

Mit Ihrer Zustimmung wird hier ein externes YouTube-Video (Google Ireland Limited) geladen.

Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit können personenbezogene Daten an Drittplattformen (Google Ireland Limited) übermittelt werden. Mehr dazu in unserer Datenschutzerklärung.

Skywater hatte 2017 ein Halbleiter-Werk vom Hersteller Cypress in Bloomington (Minnesota) übernommen, das der Foundation nun gerade recht kommt: Die dortigen 130-nm-Fertigungslinien sind für aktuelle Hochleistungs-Chips zu alt (der 130-nm-Prozess wurde 2001 etabliert), für kleinere ASICs aber genau richtig. (cm)