"Ponte Vecchio": Intel-Chefarchitekt zeigt riesige Supercomputer-GPU

Intel setzt beim GPU-Beschleuniger Xe HPC auf eine Vielzahl von Chiplets, die auf einem Träger vereint werden. Erste Beschleuniger sind für Tests bereit.

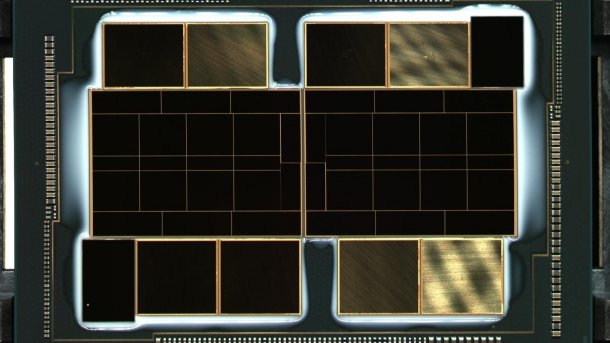

(Bild: Raja Koduri / Twitter)

Es geht voran bei Intels Prestige-GPU-Projekt mit Codenamen Ponte Vecchio alias Xe HPC: Chefarchitekt Raja Koduri teilte kürzlich über Twitter das erste Bild eines entsprechenden GPU-Beschleunigers, der aus einer Vielzahl verschiedener Silizium-Chiplets besteht und für Rechenzentren gedacht ist. Intel befindet sich in der "Power on"-Phase, bei dem erste Vorserien-GPUs aus den Produktionsstätten kommen und erstmals eingeschaltet werden.

Ponte Vecchio besteht aus mindestens vier verschiedenen Chiplet-Arten. Die fast quadratischen und nahezu nahtlos eingefügten Teile inmitten der großen Quader dürften die Compute-Tiles darstellen, die die Shader-Rechenkerne beinhalten. Intel fertigt sie selbst mit eigener 7-Nanometer-Technik, holt sich zusätzliche Kontingente aber auch von extern – vermutlich von Chipauftragsfertiger TSMC.

Videos by heise

Xe-Links, HBM, Cache

Ein selbstentworfener Interconnect verbindet die zweimal acht Shader-Cluster untereinander, von Intel Scalable Memory Fabric beziehungsweise Xe MF genannt. Die schmalen Chiplets zwischen den Compute-Tiles sowie die etwas breiteren zwischen den zwei zusammengesetzten Chips dürften die entsprechenden Links enthalten – extern gefertigt. Sie sorgen dafür, dass sich das Konstrukt wie eine einzelne GPU verhält, was bei Compute-Aufgaben besser funktioniert als bei latenzkritischen 3D-Spielen.

Die insgesamt sechs Siliziumflächen an den äußeren Rändern könnten Cache und Speicher-Controller bereitstellen. An diesen dockt Intel High-Bandwidth Memory (HBM) in Form von insgesamt acht Speicherstapeln. Das quer gestellte Die enthält entweder weiteren Cache oder I/O-Funktionen. Intel fertigt für Ponte Vecchio zudem Base-Tiles mit eigener 10-nm-Technik, die sich unter dem sichtbaren Siliziumkonstrukt befinden dürften.

(Bild: Intel)

Aufwendiges Zusammenfügen

Zum Verbinden aller Chiplets setzt Intel auf verschiedene Packaging-Techniken, darunter das 3D-Stacking Foveros und die Embedded Multi-Die Interconnect Bridge (EMIB). Das gezeigte Bild scheint derweil nachträglich bearbeitet worden zu sein: Die HBM-Stacks unten etwa wirken größer als jene unten – die mögliche Folge einer perspektivischen Korrektur.

Eigentlich wollte Intel GPU-Beschleuniger auf Basis von Ponte Vecchio noch dieses Jahr in Tausenden Stückzahlen ausliefern, unter anderem an das US-amerikanische Argonne National Lab zum Bau des Exascale-Supercomputers Aurora. Aufgrund von Verzögerungen beim eigenen 7-nm-Prozess wurde der Startschuss jedoch verschoben.

(mma)