Intel und TSMC arbeiten an Transistoren der Zukunft

Gestapelte CMOS-Transistorpärchen mit ultradünnen Kristallschichten sollen helfen, das Moore'sche Gesetz fortzuführen.

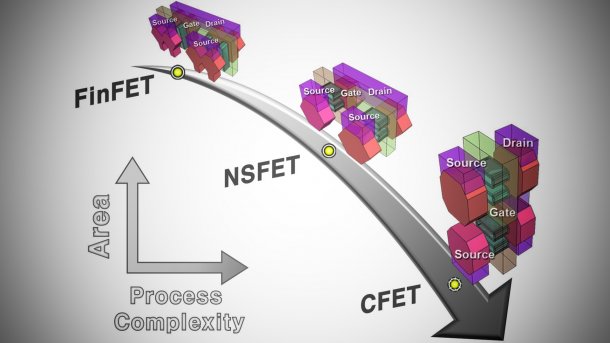

TSMC arbeitet an komplementären Feldeffekttransistoren (CFETs) für kommende Prozessoren, die auf Nanosheet-FETs (NSFETs) und die heute üblichen FinFETs folgen.

(Bild: TSMC/IEDM)

Chiphersteller wie TSMC, Intel und Samsung sowie Forschergruppen von IBM, dem belgischen IMEC und der taiwanischen Yang Ming Chiao Tung University entwickeln neue Transistorkonzepte. Sie sollen bei zukünftigen Fertigungsverfahren für Halbleiterbauelemente zum Einsatz kommen, die Strukturen von weniger als 2 Nanometern erzeugen. Unter anderem will man superdünne Kristallstrukturen nutzen, die wenige Atomlagen dicke Schichten mit besonderen elektrischen Eigenschaften ausbilden.

Auf Fachkonferenzen wie dem International Electron Devices Meeting (IEEE IEDM) präsentierten Forscher in den vergangenen Jahren immer wieder Untersuchungen an "2D"-Materialien aus Übergangsmetalldichalkogeniden (Transitional Metal Dichalcogenides, TMD) wie Molybdändisulfid (MoS2) und Wolframselenid (WSe2).

Videos by heise

Intel und TSMC planen, solche Schichten als leitende Kanäle (Channels) kommender Feldeffekttransistoren (FETs) zu nutzen. Dazu braucht man unterschiedliche Materialien, weil sich MoS2 vor allem für n-Kanal-FETs eignet, während WSe2 für p-Kanal-FETs besser ist. Dabei müssen die jeweils komplementär arbeitenden n- und p-Kanal-FETS (CMOS bedeutet Complementary Metal Oxide Semiconductor) jedoch so hergestellt werden, dass sie zueinander passende elektrische Eigenschaften haben. Hinzu kommt das Problem, dass man die dünnen Schichten in Großserie robust genug fertigen können muss, damit sie nachfolgende Produktionsschritte zuverlässig überstehen.

(Bild: TSMC/IEDM)

TSMC stellt auf dem IEDM gute Messergebnisse von n- und p-FETs mit Kanälen aus MoS2- und WSe2-Dünnschichten vor. Dabei wurde der MoS2-Kanal des n-FETs zwischen Schichten aus Hafniumoxid (HfOx) und Titannitrid (TiN) eingebracht. Außerdem zeigte TSMC eine gestapelte Schichtstruktur für einen n-FET mit MoS2-Nanosheets.

Komplementäre FET-Pärchen

Sowohl TSMC als auch Intel arbeiten an übereinandergestapelten Transistorpärchen, die wenig Siliziumfläche belegen und als CMOS-Inverter mit gemeinsamer Gate-Elektrode arbeiten: Complimentary-FETs (CFETs). Intel präsentierte einen solche CFET-Aufbau mit je drei n-FET- und p-FET-"Nanoribbons", der bereits für die Fertigung auf Wafern mit rückseitiger Stromversorgung durch das Siliziumbasismaterial hindurch ausgelegt ist. Intel nennt diese hauseigene Technik für Backside Power Delivery (BPD) "PowerVia", weil die Kontakte für die Stromversorgung als Vias durch den gedünnten Wafer hindurchführen.

(Bild: Intel/IEDM)

Das IMEC präsentiert auf der IEDM Forschungsresultate zu Backside Power Delivery. Demnach wirkt sich die Bearbeitung der Wafer-Rückseite nicht störend auf die Schichten der Oberseite aus. BPD ermöglicht es demnach wie geplant, die dickeren Leitungen für die Stromzufuhr von den Datensignalen auf der anderen Waferseite oberhalb der Transistoren zu entflechten.

Die Forscher der Yang Ming Chiao Tung University haben gemeinsam mit TSMC ein Verfahren entwickelt, um mehrere MoS2-Einzellagen übereinander zu stapeln und mit einem C-förmigen Metallkontakt zu verbinden. Daraus ergibt sich ein niedriger Kontaktwiderstand für den auf diese Art aufgebauten Gate-All-Around-(GAA-)FET mit Nanoschichten (Nanosheet-FET, NSFET).

Hören Sie dazu auch:

Empfohlener redaktioneller Inhalt

Mit Ihrer Zustimmung wird hier ein externer Podcast (Podigee GmbH) geladen.

Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit können personenbezogene Daten an Drittplattformen (Podigee GmbH) übermittelt werden. Mehr dazu in unserer Datenschutzerklärung.

(ciw)