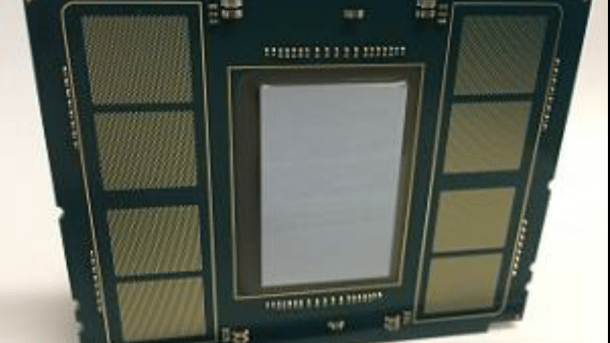

Intels Supercomputer-Beschleuniger Xeon Phi Knights Landing mit vier Reservekernen

Die ein oder andere kleine Überraschung gibts bei der schrittweisen Entblätterung der nächsten Xeon-Phi-Architektur schon, etwa die tatsächliche Zahl der physischen Kerne auf dem Chip.

Häppchenweise gibt Intel immer weitere Details zur Architektur der nächsten Generation seines Supercomputer-Coprozessors Xeon Phi bekannt. Auf der Hot-Chip-Konferenz bestätigte KNL-Chefarchitekt Avinsh Sodani nun, dass der für Ende des Jahres vorgesehene Xeon Phi x200 (Knights Landing) sogar zwei Kacheln mit insgesamt vier Kernen mehr aufweist, als bislang kundgetan wurde. Diese sind aber nicht freigeschaltet, sondern dienen der Reserve für Ausbeuteoptimierung (Yield Rate).

Die bislang bekannten 72 Arbeits-Kerne sind beim Xeon Phi Knights Landing in Kacheln (Tiles) zu zweit organisiert, die dann in einem 2D-Mesh zusammen mit den Speicher-Controllern, dem PCIe-3.4-Interface und dem DMI-Controller kommunizieren. Rein physisch befinden sich mit den zusätzlichen Kernen aber insgesamt 76 Kerne beziehungsweise 38 Kacheln auf dem Chip. Zusammen mit den beiden Speicher-Controllern und zwei PCIe/DMI-Controllern sind sie in einem 6x7-Feld angeordnet.

Theoretisch könnte man natürlich für jeden Chip so viele Kacheln freischalten wie funktionieren. Das hat Intel aber zumindest zunächst nicht vor, erklärte Sodani. Das passt auch nicht ins Mesh-Konzept, wo man unter anderem den Chip in vier virtuelle Quadranten aufteilen kann. Dann wäre es schon zweckmäßig, wenn die Kachelzahl durch vier teilbar ist.

(Bild: Intel)

(as)