AMD-CEO Lisa Su schaut in die Halbleiter-Zukunft

AMDs CEO Lisa Su hat in ihrer Keynote auf der Hot Chips die Herausforderungen der Halbleiterindustrie zusammengefasst.

AMDs CEO Lisa Su auf der Hot Chips 2019

(Bild: c't / Florian Müssig)

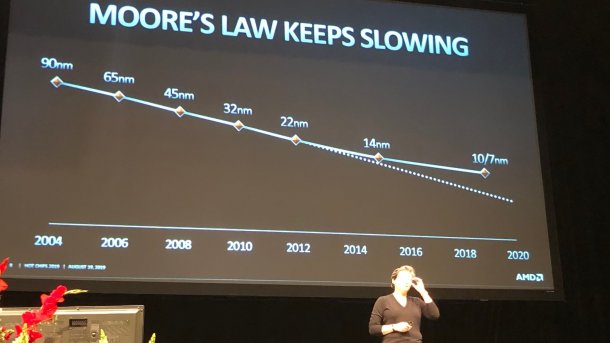

Lisa Su wollte sich in ihrem Vortrag auf der Konferenz Hot Chips zwar nicht explizit festlegen, ob Moore's Law nun tot ist oder nicht, aber es sei zumindest klar, dass Fortschritte in der Performance in den vergangenen Jahren langsamer und schwieriger geworden sind. Gleichzeitig gibt es weiterhin laufend neue Anwendungen, die mehr und mehr Rechenleistung erfordern: In der KI-Welt verdoppelte sich der Rechenbedarf teilweise alle 3,5 Monate. Aber auch bei herkömmlichen Anwendungen steigt der Bedarf – wobei Su eigentlich gar nicht kategorisieren wollte: Aus Halbleitersicht sind sich die beiden Welten sehr ähnlich, denn beide wollen riesige Datenmengen auswerten und setzen auf massive parallele Verarbeitung.

(Bild: AMD)

Feinere Fertigungsprozesse erlauben eine höhere Transistordichte und einen geringeren Energiebedarf, doch sie werden immer schwieriger zu erzielen. Das sei schade, denn in der vergangenen Dekade waren rund 60 Prozent der Performancesteigerungen neuen Fertigungsprozessen und zugehörigen Effekten zu verdanken. Künftig würden also mehr und mehr Tricks bei den Mikroarchitekturen und dem Power Management anwenden müssen.

Das sei insofern hart, weil sich die IT-Welt immer noch schnell dreht, man bei der CPU-Entwicklung aber drei bis fünf Jahre vorausschauend arbeiten müsse – mit möglichst wenig falschen Prognosen, versteht sich. Aktuell sei neben Zen 3 auch schon Zen 4 in Arbeit.

Chiplets sind die Zukunft

(Bild: AMD)

Gleichzeitig wachsen die mit immer höheren Transistorzahlen pro Die verbundenen Eigenheiten – seien es nun die Kosten pro Chip oder die Auswirkungen kleiner Fertigungsfehler. AMD habe sich deshalb schon im Jahr 2013 entschieden, nicht mehr auf große monolithische Chipdesigns zu setzen, sondern einen modularen Aufbau aus Chiplets zu wählen.

Das hat gleichzeitig den Vorteil, dass man sich je nach Chiplet den optimalen Fertigungsprozess aussuchen kann. Bei Zen-2-CPUs laufen beispielsweise nur die CPU-Kerne im modernsten Prozess (7 nm) vom Band. Der die Kerne verbindende I/O-Chip enthält hingegen analoge Komponenten, die besser in älteren, etablierteren Fertigungsprozessen funktionieren – er wird deshalb in 12 nm gefertigt.

(Bild: AMD)

Die an sich logische Herangehensweise, dass man für jedes Problem die optimale Lösung nutzen sollte, gibt es auch auf Systemebene: Manche Probleme erfordern CPUs, manche GPUs und manche wiederum Spezial-Hardware wie FPGAs oder ASICs. AMD habe zwar nicht vor, auch letztere zu entwickeln, binde sie aber gerne mit ein. Wichtig ist in diesem Fall eine möglichst rasante Anbindung, die man aktuell mit PCIe-4.0-Unterstützung bereits bieten könne.

Formel-1-Effekt

(Bild: AMD)

Auch wenn viele grundsätzliche Überlegungen aus der HPC-Server-Welt stammen, so solle man laut Su nicht vergessen, dass sie im Laufe der Zeit auch in Produkten für Endkunden ankommen – dank modularer Chiplets sogar viel schneller als früher üblich. Aktuell arbeite AMD gemeinsam mit Cray am nächsten Supercomputer der Oak Ridge National Labs namens Frontier, in dem sowohl Epyc-CPUs als auch Radeon-GPUs zusammengeschaltet werden. Wenn Frontier anno 2021 in Betrieb geht, soll er eine maximale Rechenleistung von rund 1,5 Exaflops bereitstellen. (mue)