EPI Rhea HPC: Europa-Prozessor mit 72 ARM-Kernen

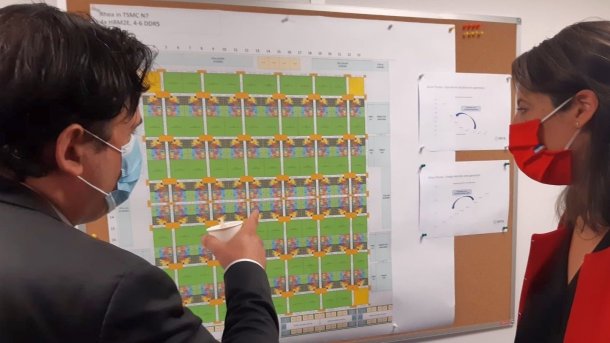

Ein Twitter-Foto einer französischen Politikerin enthüllt ein CPU-Design der European Processor Initiative, das sich etwas von der Vorplanung unterscheidet.

Der EPI-Prozessor Rhea HPC könnte 72 ARMv8-Kerne haben.

(Bild: Twitter/Alexandra Dublanche)

Im Rahmen der European Processor Inititative (EPI) entwickeln 26 Partnerfimen unter Leitung der französischen SiPearl mehrere Prozessoren für Supercomputer, autonome Autos, Rüstungstechnik und kritische Infrastrukturen (KRITIS). Eine Twitter-Meldung zum Besuch der französischen Unternehmerin und Politikerin Alexandra Dublanche am SiPearl-Hauptsitz nahe Paris verrät nun mehr Details zur ersten EPI-Prozessorversion "Rhea HPC" für künftige Exascale-Supercomputer: Auf einem Foto ist das Blockschaltbild eines 7-Nanometer-Chips mit 72 Prozessorkernen zu erkennen.

Videos by heise

Laut der EPI-Roadmap war ursprünglich für 2021 die Rhea-Familie als erste Generation (Gen 1) für Allzweckprozessoren (General Purpose Processor, GPP) geplant, zur Fertigung mit 6-Nanometer-Technik (N6) von TSMC. Rhea soll auf einer PCI-Express-Karte die EPI Common Platform (EPI CP) mit ARM- und RISC-V-Kernen für Tests und zur Software-Entwicklung bereitstellen.

(Bild: MDPI: Mario Kovač, Philippe Notton, Daniel Hofman, Josip Knezović, Uni Zagreb/SiPearl)

Das Twitter-Foto legt nun nahe, dass statt 6-Nanometer-Technik nun eher 7-Nanometer-Technik von TSMC zum Einsatz kommt. Falls die 72 sichtbaren CPU-Kerne die ARM-Kerne darstellen, dürfte es sich um welche vom Typ "Zeus" handeln: Das sind verbesserte Nachfolger des Neoverse N1 "Ares", die etwa in den Serverprozessoren Amazon Graviton2 und Ampere Altra zum Einsatz kommen.

Zeus alias Neoverse N2 soll unter anderem Daten im BFloat-16-(BF16-)Format verarbeiten, was ARM mit ARMv8.6 eingeführt hat. Rhea soll auch Scalable Vector Extensions (ARM SVE) bereitstellen. Zudem stecken in Rhea noch andere Kerne, etwa Kalray MPPA, eFPGA-Blöcke der Firma Menta, EPI-eigene Rechenbeschleuniger mit RISC-V-Technik (EPI Accelerator/EPAC) sowie dedizierte Krypto-Hardware. Ein Network-on-Chip (NoC) verknüpft die Rechenwerke; das CCIX-Interface dient zur kohärenten Anbindung externer Beschleuniger. Schließlich gibt es auch PCI Express 5.0 und Rhea hat Speichercontroller für vier HBM2E-Speicherchipstapel sowie für vier bis sechs DDR5-SDRAM-Kanäle.

(Bild: EPI/Mauro Olivieri)

In einem Paper des via MDPI veröffentlichten Open-Access-Journals Mathematical and Computational Applications (MCA) vom Juli 2020 wurde der Rhea-Start nun aber schon von 2021 auf 2022 verschoben. Ein Blockschaltbild aus diesem Paper erwähnt auch schon Funktionen wie Compute Express Link (CXL) und TITAN, die erst für die zweite EPI-CP-GPP-Generation Cronos geplant sind, die nicht vor 2023 zu erwarten ist.

(ciw)