Modernste Transistoren: IBM erprobt 2-Nanometer-Chips

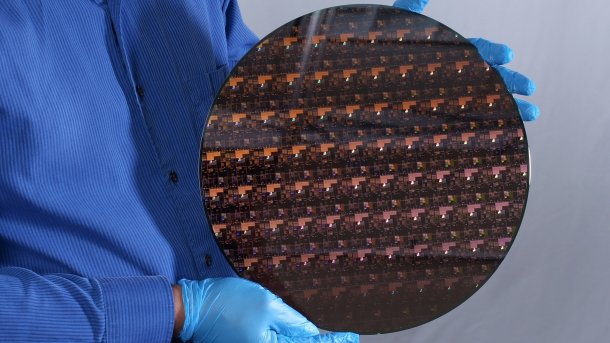

Auf den ersten gefertigten 2-nm-Chip packt IBM doppelt so viele Transistoren wie auf bisherige 5-nm-Halbleiterelemente: 333 Millionen pro Quadratmillimeter.

(Bild: IBM)

IBMs Forschungsabteilung hat auf einer Pilotanlage den ersten Halbleiterbaustein mit Strukturbreiten von 2 Nanometern gefertigt, also Technik der übernächsten Generation. In der Serienproduktion befinden sich zurzeit 5-nm-Chips, darauf folgt die 3-nm-Generation. Bis zur Serienfertigung von 2-nm-Chips werden noch mehrere Jahre vergehen.

Grafikchips und x86-Prozessoren von AMD und Intel laufen bisher bestenfalls mit 7-nm-Technik vom Fließband, etwa AMDs Ryzen-5000-CPUs beim Chipauftragsfertiger TSMC. Letzterer produziert aber auch bereits 5-nm-Chips wie Apple A14 und M1 sowie Qualcomm Snapdragon 888. Laut IBMs Ankündigung sollen 2-nm-Transistoren bei gleicher Leistungsaufnahme 45 Prozent mehr Performance bringen als die besten 7-nm-Transistoren oder bei gleicher Performance 75 Prozent weniger Energie umsetzen.

Massig Transistoren

Die Nanometer-Angaben der Chiphersteller beschreiben leider längst keine konkreten Strukturbreiten mehr, sondern stehen als Klassenbezeichnungen für fortlaufende Verkleinerungen der Transistoren. Nach eigenen Angaben quetscht IBMs 2-nm-Technik 50 Milliarden Transistoren auf eine fingernagelgroße Chipfläche. Die Webseite Anandtech hat in Erfahrung gebracht, dass damit eine Größe von 150 mm² gemeint ist – entsprechend passen im Bestfall etwa 333 Millionen Transistoren auf jeden Quadratmillimeter Silizium. Üblicherweise bezieht sich dieser Idealwert auf besonders dicht gepackte 6T-SRAM-Zellen aus je sechs Transistoren (6T). Transistoren für andere Funktionen wie Logik- oder Analogblöcke fallen oft größer aus.

Videos by heise

Zum Vergleich: Wikichip hat verschiedene 7-nm-Halbleiterelemente analysiert und kam bei TSMC auf bis zu gut 91 Millionen Transistoren/mm² und bei Samsung auf 95 Millionen. Chips, die bei TSMC mit 5-nm-Strukturen entstehen, etwa Apples M1-Prozessor, liegen Schätzungen zufolge zwischen 130 und 230 Millionen Transistoren/mm². Mit dichter gepackten und effizienteren Fertigungsprozessen lassen sich beispielsweise schnellere Prozessoren und Grafikkarten bauen.

IBM verwendet eine Form der "Gate All-Around"-(GAA-)Technik zum Aufbau der Transistoren, im Firmensprech Nanosheets genannt. Der leitende Kanal des Feldeffekttransistors (FET) ist bei GAA-FETs allseits von der Gate-Elektrode umgeben. TSMC will ähnliche Technik ab der eigenen 2-nm-Generation einsetzen, Samsung ab dem Schritt auf 3 nm.

IBMs 2-nm-Technik (5 Bilder)

(Bild: IBM)

Forschungsprojekt

Bisher handelt es sich bei der 2-nm-Technik von IBM um ein Entwicklungsprojekt. Die Serienproduktion von 2-nm-Prozessoren wäre frühestens ab dem Jahr 2025 in Zusammenarbeit mit Samsung oder Intel realistisch. Zusammen mit Samsung und Globalfoundries unterhält IBM eine Forschungsallianz, Globalfoundries ist jedoch aus dem Rennen der modernsten Fertigungsprozesse ausgeschieden. Die Partnerschaft mit Intel steckt noch in den Kinderschuhen.

Im Jahr 2017 hat IBM bereits den ersten 5-nm-Chip mit GAA-Transistoren gezeigt. Vier Jahre später erscheint jedoch gerade einmal die Server-CPU Power10 mit 7-nm-Strukturen von Samsung – IBM ist in dieser Generation später dran als Konkurrenzunternehmen wie AMD und Nvidia.

(mma)