KI-Beschleuniger in SSD-Bauform U.2

Western Digital kündigt einen FPGA-Beschleuniger für Machine Learning an, der mit Zebra-Technik von Mipsology und einem Xilinx ZYNQ arbeitet.

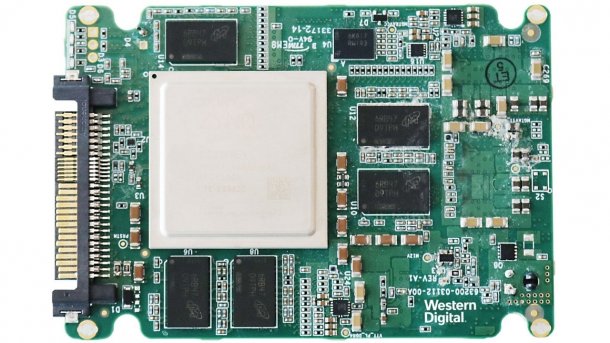

Machine Learning Accelerator in U.2-Bauform von Western Digital (WD)

(Bild: WD)

Western Digital (WD) empfiehlt, zur Beschleunigung von Machine-Learning-(ML-)Algorithmen statt einer stromdurstigen GPU lieber einen effizienteren FPGA-Chip zu nutzen. Gemeinsam mit Mipsology bringt WD dazu einen ML-Beschleuniger mit einem Xilinx ZYNQ UltraScale+ XCZU7EV heraus, der die Bauform einer U.2-SSD hat. Der Machine Learning Accelerator (MLA) verwendet auch den PCI-Express-Anschluss der SFF-8639-Buchse der U.2-Bauform und soll weniger als 20 Watt Leistung aufnehmen.

Die "Zebra"-Technik von Mipsology für KI-Inference ist bereits bei Amazon AWS nutzbar. Der WD-MLA kann Modelle verarbeiten, die in TensorFlow, Caffe, Caffe2 oder MXNET geschrieben wurden. Laut Mipsology ist kein neues Training nötig. In ResNet50 soll der Beschleuniger 239 Frames pro Sekunde schaffen, in Googlenet 561.

WD will den MLA auf der Fachmesse embedded world 2019 vorführen (Stand 3A-429, Halle 3A). (ciw)