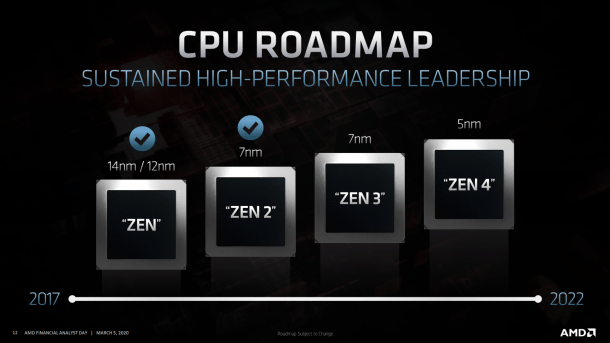

AMD Ryzen und Epyc: Zen-4-Prozessoren kommen mit 5-nm-Technik

In den kommenden Jahren wird das Stapeln von verschiedenen Siliziumchips übereinander wieder zum Thema – AMD forscht weiter am 3D-Stacking.

(Bild: AMD)

AMD setzt bei der fünften Zen-Prozessorgeneration erneut auf neue Chipfertigungstechnik und eine überarbeitete Architektur. Modelle mit Zen 4 sollen spätestens 2022 erscheinen und die Transistorstrukturen von 7 auf 5 Nanometer schrumpfen.

Gleichzeitig versprach AMDs Chief Technical Officer (CTO) Mark Papermaster auf dem gestrigen Financial Analyst Day neuen Speicher, vermutlich DDR5 einhergehend mit neuen CPU-Fassungen.

CPU-Chiplets der aktuellen Zen-2-Generation (Ryzen 3000, Epyc 7002) lässt AMD beim weltweit größten Chipauftragsfertiger TSMC mit dessen 7-nm-Technik produzieren. TSMCs 5-nm-Prozess soll bei gleicher Leistungsaufnahme 15 Prozent höhere Taktfrequenzen erlauben oder bei gleichen Taktfrequenzen 30 Prozent effizienter laufen. Vor Zen 4 erscheinen noch AMDs Prozessoren mit der CPU-Architektur Zen 3, die den verbesserten 7-nm-Prozess N7+ (statt N7) mit extrem-ultravioletter Belichtung (EUV) verwenden sollen. Erste Zen-3-Modelle hat AMD für das Jahr 2020 angesetzt.

Gestapelte Chips

Während Intel seine Chipstapeltechnik bereits werbewirksam Foveros getauft hat und dieses Jahr mit Lakefield einen ersten entsprechenden Prozessor bringt, arbeitet auch AMD hinter den Kulissen an gestapelten Chips. Konkret zeigte Papermaster ein Schaubild mit vier einlagigen Chiplets in der Mitte und vier weiteren vierlagigen, die seitlich angeordnet sind. Die Kombination nennt AMD X3D-Stacking als Kombination aus 2,5D- (Chips auf einem Träger nebeneinander) und 3D-Stapelung (Chips übereinander).

x

Das Schaubild erinnert an ein AMD-Paper von Anfang 2017, in dem AMD einen simulierten Exascale-Kombiprozessor vorstellte: In der Mitte saßen CPU-Chiplets und außen GPU-Chiplets mit aufgesetzten HBM-Speicherstapeln. Das Gesamtkonstrukt kam damals auf 32 CPU-Kerne, 24.576 Shader-Einheiten und 256 GByte Speicher auf einem Träger – offensichtlich für Rechenzentren und nicht etwa für Spieler.

(Bild: AMD)

(mma)