CCIX: Schnittstelle für Hardware-Beschleuniger

AMD, ARM, IBM, Qualcomm, Xilink, Huawei und Mellanox spezifizieren im CCIX-Konsortium einen gemeinsamen Standard für die Cache-kohärente Verbindung zwischen Prozessoren und spezialisierten Beschleunigern.

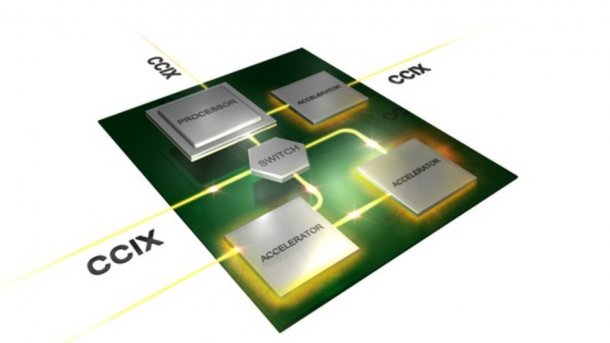

CCIX verknüpft CPUs und Beschleuniger

(Bild: CCIX Consortium)

Statt immer mehr gleichartiger Prozessorkerne kommen in Rechenzentren zunehmend hybride Systeme zum Einsatz, bei denen Spezialprozessoren als Beschleuniger oder besonders effiziente Rechenwerke arbeiten. Aus praktischen Gründen kommt als Schnittstelle zwischen CPU und Beschleuniger dabei meistens PCI Express zum Einsatz, denn PCie ist überall schon eingebaut. Für Cache-kohärente Verbindungen will das CCIX-Konsortium nun aber einen neuen, besonders schnellen und latenzarmen Link spezifizieren.

Die Liste der Gründungsmitglieder – AMD, ARM, IBM, Qualcomm, Xilink, Huawei und Mellanox – deckt sich wohl nicht zufällig an drei Stellen mit der der HSA Foundation für eine Heterogeneous System Architecture. In beiden Vereinen fehlen ebenso vorhersehbar Intel und Nvidia: Intel als Server-Primus kocht mit Omni Path und QPI ein eigenes Süppchen und hat sich einen FPGA-Spezialisten mit Altera gleich einverleibt. Nvidia arbeitet mit IBM an CAPI beziehungsweise NVLINK: Darüber sollen künftig OpenPOWER-Prozessoren und Tesla-Beschleuniger miteinander kommunizieren.

Viele Anläufe

Es gab in den vergangenen Jahren schon mehrere Anläufe, schnelle und kohärente Interconnects als universelle Beschleuniger-Schnittstellen zu etablieren. Für AMDs HyperTransport gab es mit HTX auch eine Steckkarten-Version, zudem war Torrenza geplant, Intel wollte den Frontsidebus öffnen und mit Geneseo eine Kohärenz-Erweiterung für PCIe entwickeln.

Auch RapidIO soll eine kohärente Erweiterung für Coprozessoren bekommen, daran werkelt eine Gruppe unter anderem mit AMD, ARM und Xilinx seit Ende 2014. Dafür hat ARM etwa angekündigt, das Protokoll des für die interne Verbindung von System-on-Chip-(SoC-)Bausteinen gedachten AMBA-Bus auf RapidIO zu mappen. (ciw)