Flash Memory Summit: 48-lagige Chips für 16-TByte-SSD

Samsung verdoppelt die Speicherkapazität pro Flash-Chip und will daraus größere und sparsamere SSDs bauen.

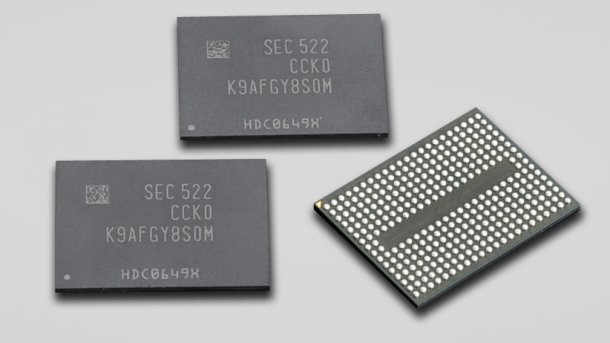

Samsung verdoppelt die Kapazität seiner Flash-Chips in 3D-VNAND-Bauweise auf 256 GBit, sprich 32 GByte. Dazu packt der Chiphersteller nun 48 statt zuvor 32 Flash-Zellen übereinander. Bei 3D V-NAND handelt es sich erst einmal nicht um Stapel aus mehreren Silizium-Dies, sondern tatsächlich um ein Silizium-Die in dem die Zellen nicht mehr planar in der Ebene angeordnet, sondern als dreidimensionale Säulen gebaut werden.Unabhängig davon kann man mehrere solcher Dies übereinander stapeln, um noch höhere Kapazitäten in einem Chip-Gehäuse unterzubringen.

Samsung spricht von einer 3D-CTF-Struktur (Charge Trap Flash). Im ganzen Chip gibt es rund 1,8 Milliarden solcher Säulen, jede davon enthält 48 Zellen von denen jede wiederum drei Bit speichert. Samsung nennt das 3 Bit Multi Level Cell (MLC), andere sprechen von Triple Level Cells (TLC). Vor etwa einem Jahr hatte Samsung diese Triple-Level-Cells bei 3D-V-NAND eingeführt. Verglichen mit den 128-GBit-Vorgängern sollen die neuen Chips 30 Prozent weniger Energie brauchen und sich 40 Prozent effektiver herstellen lassen. Anders ausgedrückt: Es bestehen gute Chancen, dass die nächste Generation von 2,5:"-SSDs nicht nur größer, sondern auch billiger wird.

Zum Einsatz kommen sollen das erstmals in Form eines Updates der Samsung 850 Evo. Für Kunden ändert sich damit wenig – nur wird die neue 850 wohl etwas sparsamer als die alte. Dagegen soll die Server-SSD PM1633a, die Samsung auf demFlash Memory Summit in Aussicht gestellt hat, einen Kapazitätsrekord aufstellen: 15,36 TByte. Preise und Einführungstermin verrät Samsung noch nicht, träumt aber schon von einem Rack-Einschub für Rechenzentren mit 48 solcher SSDs und einer Gesamtkapazitätvon 768 TByte sowie bis zu 2 Millionen Iops.

(bbe)