Nvidia Hopper: Nächste GPU-Generation mit 80 GByte HBM3-Speicher und 3 TByte/s

Nvidias kommende GPU-Generation Hopper protzt mit hohen Transferraten und viel Speicher – das zielt auf aufwendige KI-Berechnungen und Sprachverarbeitung.

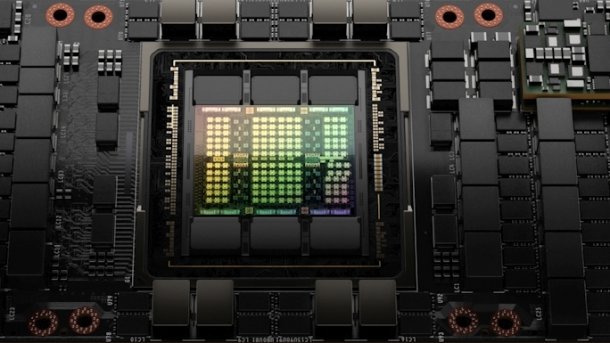

Nvidia Hopper: H100-GPU

(Bild: Nvidia)

Nvidia hat die Grafikchip-Architektur "Hopper" vorgestellt, die auf den Einsatz in Rechenzentren zugeschnitten ist. Hopper soll sich besonders gut für Berechnungen neuronaler Netze, fürs High Performance Computing (HPC) und für die Echtzeit-Sprachdatenverarbeitung eignen. Im Vergleich zur Vorgänger-Architektur "Ampere" liefert Hopper deutlich mehr Rechenleistung und bringt neue Funktionen, die unter anderem auf Datensicherheit zielen. Verfügbar sein sollen erste Chips in dritten Quartal des Jahres 2022 – Preise handelt Nvidia jeweils mit Rechenzentrumsbetreibern aus.

Videos by heise

Nvidia lässt den aus 80 Milliarden Transistoren bestehenden H100-Chip beim taiwanischen Auftragsfertiger TSMC herstellen – mit 4-nm-Strukturen (Prozess N4). Zum Vergleich: Der ebenfalls von TSCM gefertigte Ampere setzt sich aus 54 Milliarden Transistoren zusammen (7 nm). Durch den feineren Fertigungsprozess konnte Nvidia die Packdichte bei Hopper erhöhen. Hinsichtlich der reinen Geschwindigkeit soll H100 zwischen dreimal (FP16, FP64, TF32) beziehungsweise sechsmal (FP8) so schnell sein wie ein A100.

Mehr Speicher und höhere Leistungsaufnahme

(Bild: Nvidia)

Als erste HPC-GPU setzt H100 auf den Stapelspeicher HBM3 – und erreicht dadurch eine Datentransferrate von insgesamt 3 TByte pro Sekunde (A100: 1,6 TByte/s). Den Speicherausbau hat Nvidia im Vergleich zu Ampere A100 auf insgesamt 80 GByte verdoppelt. Auch die Datentransferrate der PCIe-Anbindung wurde verdoppelt: PCIe 5.0 schafft rund 4 GByte/s statt wie PCIe 4.0 knapp 2 GByte/s pro Datenleitung – derzeit ebenfalls ein GPU-Alleinstellungsmerkmal von Hopper.

Deutlich angestiegen ist den Spezifikationen zufolge die Leistungsaufnahme: Während A100 als SXM-Version für Server mit 400 Watt auskommt, gibt Nvidia für den H100-SXM satte 700 Watt an – also 75 Prozent mehr. Auch eine Version in der Bauform einer PCIe-Einsteckkarte (Add-In Card, AIC) soll kommen, die bis zu 350 Watt elektrische Energie aufnehmen soll.

| H100 SXM5 | H100 PCIe | A100 (SXM) | Tesla V100 | Tesla P100 | Tesla M40 | Tesla K40 | |

| GPU | H100 (Hopper) | H100 (Hopper) | A100 (Ampere) | GV100 (Volta) | GP100 (Pascal) | GM200 (Maxwell) | GK110 (Kepler) |

| SMs | 132 | 114 | 108 | 80 | 56 | 24 | 15 |

| TPCs | 62 | 57 | 54 | 40 | 28 | 24 | 15 |

| FP32 Cores / SM | 128 | 128 | 64 | 64 | 64 | 128 | 192 |

| FP32 Cores / GPU | 15872 | 14592 | 6912 | 5120 | 3584 | 3072 | 2880 |

| FP64 Cores / SM | 64 | 64 | 32 | 32 | 32 | 4 | 64 |

| FP64 Cores / GPU | 8448 | 7296 | 3456 | 2560 | 1792 | 96 | 960 |

| Tensor Cores / SM | 4 | 4 | 4 | 8 | -- | -- | -- |

| Tensor Cores / GPU | 528 | 456 | 432 | 640 | -- | -- | -- |

| GPU Boost Clock | k. A. | k. A. | 1410 | 1455 MHz | 1480 MHz | 1114 MHz | 810/875 MHz |

| Peak FP32 TFLOPS | 60 | 48 | 19,5 | 15 | 10,6 | 6,8 | 5,04 |

| Peak FP64 TFLOPS | 30 | 24 | 9,7 | 7,5 | 5,3 | 2,1 | 1,68 |

| Peak Tensor Core TFLOPS | 500 / 1000 | 400 / 800 | 156 (TF32) / 312 (TF32 Structural Sparsity) | 120 (Mixed Precision) | -- | -- | -- |

| Speicher | 5120 Bit HBM3 | 5120 Bit HBM2e | 5120 Bit HBM2 | 4096-bit HBM2 | 4096-bit HBM2 | 384-bit GDDR5 | 384-bit GDDR5 |

| Speichergröße | 80 GByte | 80 GByte | 40 GByte | 16 GByte | 16 GByte | bis zu 24 GByte | bis zu 12 GByte |

| TDP | 700 | 350 | 400 Watt (SXM) | 300 Watt | 300 Watt | 250 Watt | 235 Watt |

| Transistoren (Mrd.) | 80 Mrd. | 80 Mrd. | 54 Mrd. | 21,1 Mrd. | 15,3 Mrd. | 8 Mrd. | 7,1 Mrd. |

| GPU Die Size | 814 mm² | 814 mm² | 826 mm² | 815 mm² | 610 mm² | 601 mm² | 551 mm² |

| Fertigung | 4 nm (4N) | 4 nm (4N) | 7 nm | 12 nm FFN | 16 nm FinFET+ | 28 nm | 28 nm |

(Bild: Nvidia)

Beschleunigung von Echtzeit-Sprachverarbeitung

Durch die "Transformer-Engine" soll Hopper besonders effektiv bei der Echtzeit-Verarbeitung und Übersetzung natürlicher Sprache über das von Google entwickelte, populäre Transformer-Deep-Learning-Modell sein. Um sowohl Leistung als auch Genauigkeit zu gewährleisten, kombiniert Nvidia dynamisch 8- und 16-Bit-Datenformate. Der Transformer verwendet keinen Recurrent-Ansatz wie die meisten Systeme zur maschinellen Übersetzung, sondern verarbeitet alle Worte parallel und bindet außerdem über einen speziellen Mechanismus den Kontext von Worten ein, die innerhalb der Sequenz weiter entfernt sind – und ist entsprechend parallelisierbar.

Über spezielle Confidential-Computing-Funktionen, einer Kombination aus Hard- und Software (gesicherte VM), will Nvidia die Sicherheit der in Echtzeit verarbeiteten Daten gewährleisten. Dies soll auch separat für einzelne Nutzer-Instanzen funktionieren – H100 erlaubt über Secure Multi-Instance bis zu sieben Cloud-Tenants pro H100-GPU, die jeweils einer T4-GPU entsprechen sollen. Auch A100 ließ schon sieben Instanzen pro GPU zu. Über NVLink 4.0 können verschiedene H100-Chips untereinander mit 900 GByte/s kommunizieren – eine Steigerung um 50 Prozent im Vergleich zum A100.

DGX H100 mit acht Hopper-Karten

(Bild: Nvidia)

Als erstes Hopper-System kündigte Nvidia den DGX H100 an. Er enthält acht H100-Karten, die eine Rechenleistung von 32 Tensor-Petaflops bei KI-Berechnungen (FP16) und 0,5 PFlops bei FP64-Berechnungen erreichen sollen – im Vergleich zum DGX A100 eine sechs- beziehungsweise dreifache Steigerung. Überdies stellte Nvidia noch das Serversystem DGX SuperPOD mit 32 DGX H100 vor, Preise und konkrete Verfügbarkeitstermine verlautbarte Nvidia für diese Systeme jedoch nicht.

Instanzen auf H100-Basis wollen Nvidia zufolge die Cloud-Dienstleister Alibaba Cloud, Amazon Web Services, Baidu AI Cloud, Google Cloud, Microsoft Azure, Oracle Cloud und Tencent Cloud anbieten. Server mit H100-Beschleunigern sollen künftig unter anderem von Atos, Boxx Technologies, Cisco, Dell, Fujitsu, Gigabyte, H3C Hewlett Packard Enterprise, Inspur, Lenovo, Nettrix und Supermicro kommen.

(mfi)