RISC-V: 1000-Kern-Beschleuniger, Server-Karte und Effizienz-Champion

Esperanto bringt einen KI-Beschleuniger mit RISC-V, Intensivate eine Mikroserver-Karte, Magic Micro den effizientesten Kern und Hacker "öffnen" einen WLAN-Chip.

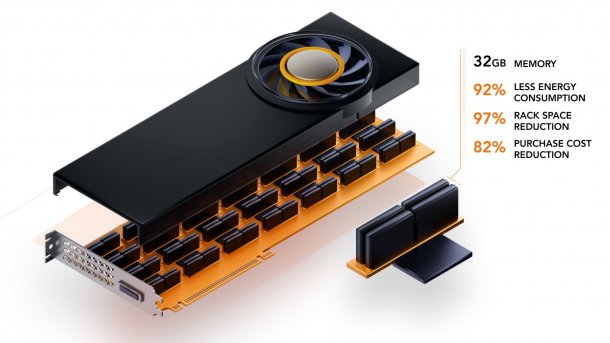

Intensivate IntenScale mit 21 RISC-V-Kernen

(Bild: Intensivate)

Am heutigen Dienstagabend startet der virtuelle RISC-V Summit 2020. Die Firma Esperanto Technologies des einstigen Transmeta-Gründers Dave Ditzel stellt dort einen KI-Beschleuniger für PCI-Express-Karten mit 1000 RISC-V-Kernen vor. Zum Einsatz kommen die bereits 2017 avisierten starken ET-Maxion-Kerne sowie sparsame ET-Minion-Kerne, die zusätzliche KI-Rechenwerke haben.

Das Unternehmen Intensivate stellt die PCIe-Karte IntenScale mit 21 RISC-V-Kernen (von SiFive) vor, die jeweils als eigene Mikroserver mit je 32 GByte RAM agieren.

Videos by heise

Im Vorfeld des RISC-V Summit kündigte das US-Unternehmen Micro Magic den nach eigenen Angaben energetisch effizientesten RISC-V-Kern überhaupt an. Im Mikrocontroller-Benchmark EEMBC Coremark liefert ein Protoyp demnach 110.000 Coremark-Punkte pro Watt bei 3 GHz. Alternativ erreicht dieser "64-Bit-RISC-V"-Kern die verblüffend hohe Taktfrequenz von 5 GHz und errechnet dabei 13.000 Coremark-Punkte. Zum Vergleich: Die vier ARM-Cortex-A53-Kerne des Broadcom BCM2837 auf einem Raspberry Pi 3B schaffen bei 1,2 GHz zusammen 13.717 Coremark-Punkte. Der vier x86-Kernen von "Atom"-Typ im älteren Intel Celeron J1900 liefern zusammen rund 30.000 Coremark-Punkte.

Weil noch viele Angaben zum Micro-Magic-RISC-V-Kern fehlen, ist eine Einordnung der Firmenangaben schwierig. So ist etwa unklar, ob der Kern Gleitkomma-Rechenwerke enthält oder die für Linux empfohlene Spezifikation RV64GC erfüllt. Der Coremark verwendet vorwiegend Integer-Befehle.

Offener WLAN-Chip

(Bild: Bouffalo Lab)

Die chinesische Firma Bouffalo Lab (博流智能科技) hat den WLAN- und Bluetooth-Mikrocontroller BL602 (BL604 mit 40 Pins) mit 32-Bit-RISC-V-Kern entwickelt. Die Firma Pine64 hat nun einen "Nutcracker"-Wettbewerb ausgerufen, um die Firmware des BL602 durch Reverse Engineering offenzulegen. Ziel ist der WLAN- und Buetooth-Adapter "PineCone" mit komplett offener Software, also BLOB-frei.

Mit dem Espressif ESP32-C3 kommt aber noch ein weiterer WLAN-/BLE-Mikrocontroller mit RISC-V-Kern auf den Markt. Es könnten noch weitere folgen, weil das Unternehmen CEVA derartige "RivieraWaves"-WLAN-/BLE-Funktionsblöcke mit RISC-V-Kernen als Zulieferer entwickelt. Espressif nutzt beispielsweise die BLE-Technik von CEVA im ESP32.

(ciw)