RISC-V-Core von Alibaba offengelegt

Nach Western Digital (SweRV) und Google (OpenTitan) legt auch die Alibaba-Chip-Sparte T-Head das Design ihres RISC-V-Mikrocontrollers Wujian via GitHub offen.

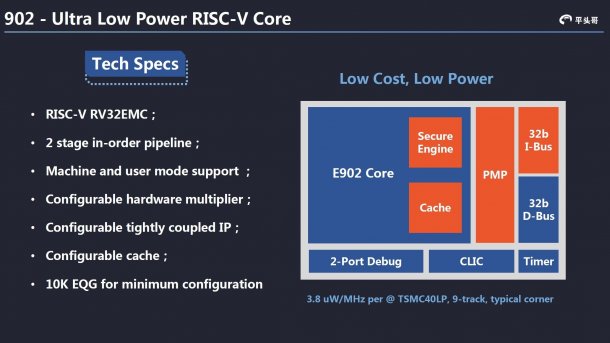

RISC-V-Kern T-Head E902

(Bild: Alibaba/T-Head)

Die offene Befehlssatzarchitektur RISC-V ermöglicht es, das Design kompletter Systems-on-Chip offenzulegen – also nicht bloß den Entwurf der eigentlichen Rechenwerke, sondern auch das von daran angeschlossenen Funktionsblöcken wie Timer, GPIOs, PWMs und UARTs.

Die Chip-Sparte T-Head der chinesischen Handels- und Cloud-Plattform Alibaba hat nun bei GitHub Teile des Mikrocontrollers Wujian 100 offengelegt, in dem der 32-Bit-RISC-V-Kern 902 steckt. Der Verilog-Code soll es ermöglichen, den wujian100_open in Verilator zu simulieren und auf einem FPGA zu emulieren. Im Unterverzeichnis doc findet sich auch ein Word-Dokument mit Spezifikationen des Wujian 100.

Laut einer Präsentation von T-Head ist eine Besonderheit der Wujian-MCUs, dass sie bereits ein Trusted Execution Environment (TEE) enthalten. Das ist ein geschützter Bereich beispielsweise zur Verarbeitung kryptografischer Schlüssel, ähnlich wie ARM TrustZone. Der TEE-Teil des Wujian 100 scheint im GitHub-Repository zu fehlen.

(Bild: Alibaba/T-Head)

Laut T-Head (das steht für Pingtouge, also Honigdachs) sollen die hauseigenen Mikrocontroller nach RV32EMC-Spezifikation unter FreeRTOS oder Alibabas AliOS laufen. Sie sind für IoT-Geräte mit sicherer Anbindung an die Alibaba-Cloud gedacht, ähnlich wie es Amazon mit der FreeRTOS-Infrastruktur, Microsoft mit Azure Sphere und Google etwa mit dem KI-Chip Coral Edge TPU vorhaben.

Offene RISC-V-Entwürfe bei GitHub

Vor einigen Monaten hatte bereits Western Digital (WD) seinen SweRV-Kern offengelegt, das Repository liegt mittlerweile in Version 1.4 unter dem Dach der Chips Alliance.

Im lowRISC-Repository bei GitHub findet sich wiederum Googles Sicherheitschip OpenTitan mit dem RISC-V-Kern Ibex, der ursprünglich von der ETH Zürich entwickelt wurde.

Schon erhältlich etwa auf dem Sipeed Longan Nano ist der RISC-V-Mikrocontroller GD32V der chinesischen Firma GigaDevice mit dem RV32-Kern Nuclei Hummingbird E203, der ebenfalls bei GitHub veröffentlicht ist.

Mehr zum Thema RISC-V bei heise+:

- RISC-V: Das Potenzial der offenen Prozessorarchitektur

- Erste Schritte mit dem RISC-V-Mikrocontroller-Board Sipeed Longan Nano

(ciw)