2 Nanometer: Diese Verbesserungen erwartet TSMC

Ab 2025 will TSMC Chips mit Strukturbreiten von 2 Nanometern produzieren. Zudem kommen die neuen 3-nm-Prozesse N3P und N3X.

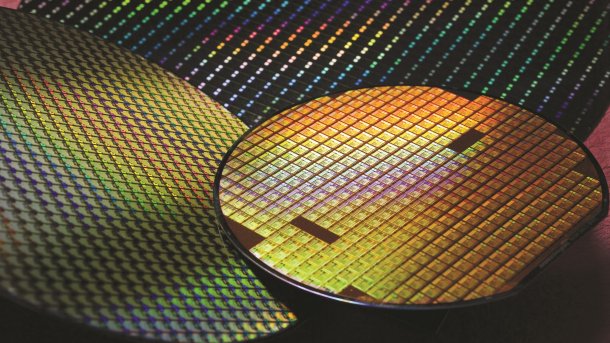

(Bild: Taiwan Semiconductor Manufacturing Co., Ltd.)

Der Chipauftragsfertiger TSMC befindet sich bei der Entwicklung seiner 2-Nanometer-Prozessgeneration im gesteckten Zeitrahmen. Aktuell tourt der Hersteller mit dem Technology Symposium, inklusive aktuellen Einblicken in die Prozessentwicklung.

Ab Ende 2025 will TSMC Chips mit 2-nm-Strukturen in Serie produzieren. Traditionell ist Apple der erste große Abnehmer für iPhone- und MacBook-Prozessoren.

Bisher nannte TSMC nur allgemeine Projektionen für die sogenannten PPA-Werte. Das steht für Performance, Power, Area und gibt einen groben Überblick über die Verbesserungen eines neuen Fertigungsprozesses.

Videos by heise

Inzwischen gibt es konkretere Zahlen anhand einer Implementierung in einem Smartphone-Prozessor, berechnet für einen ARM-CPU-Kern vom Typ Cortex-A715: Verglichen mit dem 3-nm-Prozess N3E soll die Geschwindigkeit dank kürzerer Schaltzeiten bei gleicher elektrischer Leistungsaufnahme um gut 16 Prozent steigen. Alternativ kann die elektrische Leistungsaufnahme bei gleicher Geschwindigkeit um 37 Prozent sinken. Die Transistordichte soll mindestens um den Faktor 1,15 steigen.

Der Vergleich gilt für High-Performance-Bibliotheken, wenn die Transistoren des CPU-Kerns zwei bis drei Finnen hoch sind. Bei Standardzellen mit einer bis zwei Finnen soll der Vorsprung 13 Prozent (Geschwindigkeit) beziehungsweise 33 Prozent (Leistungsaufnahme) betragen.

GAAFETs lösen FinFETs ab

Mit N2 führt TSMC Transistoren mit einem "Gate All Around"-Aufbau ein – sogenannte GAAFETs als Ablöse für FinFETs, vom Hersteller selbst Nanosheets genannt. Samsung ist diesen Schritt bereits mit seiner 3-nm-Generation gegangen, hat bis dato aber keinen großen Kunden für 3-nm-Chips verkündet. Intel will die Technik unter dem Namen RibbonFETs mit der 20A-Generation schon im Jahr 2024 einführen, wenn alles nach Plan läuft.

Der neue Aufbau ist notwendig, um die Transistoren weiter zu schrumpfen. TSMC und Intel koppeln den Umstieg an neue Lithografie-Systeme, die mit extrem-ultravioletten Wellenlängen bei hoher numerischer Apertur belichten (High-NA EUV). Weil diese Maschinen höher sind als bisherige EUV-Systeme, erfordern sie neue Halbleiterwerke. Ab 2024 will ASML die High-NA-EUV-Systeme ausliefern – Intel hat sich die ersten Kontingente gesichert.

Eine weitere Gemeinsamkeit ist der Plan, Chips künftig unterseitig mit Strom zu versorgen: Auf der Oberseite verlaufen die Signalverbindungen, auf der Unterseite erfolgt die elektrische Verdrahtung. Dieser Schritt soll die Signalqualität und die Spannungsversorgung verbessern, indem ungewollte Spannungsabsenkungen (IR Drops) verringert werden.

TSMC spricht konkret von einem zusätzlichen 10- bis 12-prozentigen Geschwindigkeitszuwachs durch die Backside Power Rails. Logikblöcke innerhalb eines Chipdesigns könnten um weitere 10 bis 15 Prozent schrumpfen. Die Technik ist vorrangig für High-Performance-Chips gedacht, also etwa CPUs und GPUs, und soll 2026 eingeführt werden.

(Bild: Taiwan Semiconductor Manufacturing Co., Ltd., via SemiWiki)

Neue 3-nm-Prozesse

Bis dahin kommt eine ganze Reihe neuer 3-nm-Prozesse. Die Massenproduktion von N3E soll im zweiten Halbjahr 2023 anlaufen. Aufgrund einer höheren Flexibilität bei den Designregeln wird eine höhere Verbreitung als bei N3 erwartet. Zusätzlich soll die Geschwindigkeit um 5 Prozent steigen. N3P legt um weitere 5 Prozent zu. Alternativ können Firmen Verbesserungen in eine 5-10 Prozent reduzierte elektrische Leistungsaufnahme investieren. Die Transistordichte soll um 4 Prozent steigen.

N3X ist für High-Performance-Chips mit höheren Spannungen gedacht. Bei 1,2 Volt soll die Geschwindigkeit noch einmal um weitere 5 Prozent steigen. Verglichen mit N3 läge das Performance-Plus somit bei 15 Prozent. Die Serienproduktion in N3P hat TSMC für das zweite Halbjahr 2024 angesetzt, N3X folgt im Jahr 2025. Auch in der 2-nm-Generation soll es N2P- und N2X-Ableger geben.

Gerüchteweise wollen AMD und Nvidia auf N3X warten, bis die auf TSMCs 3-nm-Generation umsteigen. Bis dahin sollen es 5-nm-basierte Fertigungsprozesse, einschließlich N4, richten.

Auf N3P basierend entwickelt der Chipauftragsfertiger auch die Automotive-spezifischen Prozesse N3AE (N3 Auto Early) und N3A (N3 Auto Ready). TSMC will mit Autoherstellern für eine umfassende Zertifizierungskette zusammenarbeiten, was im Falle von N3A aber erst 2026 in einer Serienproduktion münden wird. Gedacht ist die Technik etwa für autonom fahrende Autos.

(mma)