Konsortium für verteilten Server-Speicher - ohne Intel

Gen-Z von AMD, ARM, Cray, Dell, HPE, Micron, Xilinx und anderen tritt gegen Intels proprietären Interconnect Omni-Path und 3D XPoint an.

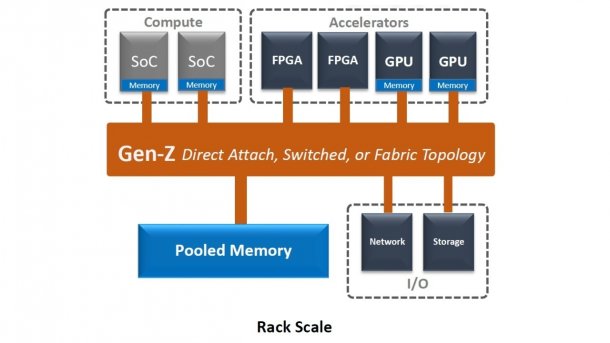

Gen-Z verknüpft Prozessoren, FPGAs und Hardware-Beschleuniger mit Speicher-Pools.

(Bild: Gen-Z Consortium)

Gen-Z: So heißt eine kommende Spezifikation, die schnellen flüchtigen und nichtflüchtigen Speicher in heterogenen Systemen aus Prozessoren und Hardware-Beschleunigern koppeln soll. Für Gen-Z haben sich die CPU-, GPU- und FPGA-Entwickler ARM, AMD und Xilinx mit den Server-Herstellern Dell, HPE und Huawei sowie mit den DRAM- und Flash-Produzenten Micron, Samsung und SK Hynix und den I/O-Spezialisten Broadcom und IDT zusammengetan.

Wer fehlt, ist Intel: Künftige Xeons, Xeon-Phi-Chips, 3D-XPoint-Speicher und später wohl auch Stratix-FPGAs dürften Intels Omni-Path nutzen beziehungsweise bekommen es eingebaut. So gesehen ist Gen-Z als offener Standard wohl auch ein Konter gegen Intels proprietäre Technik, bei der die Omni-Path Architecture (OPA, früher Omni-Scale) Teil der Scalable System Framework Architecture (SSF) ist.

[Update:] Bei Gen-Z fehlt allerdings auch der Name Nvidia und IBM ist lediglich Mitglied, nicht aber Teil des Boards, welches das Gen-Z-Konsortium steuert [/Update]: OpenPOWER-Systeme sollen künftig Nvidia-Tesla-Beschleuniger per CAPI/NVLINK anbinden. IBM verfolgt das Konzept von Storage-Class Memory (SCM), einer nichtflüchtigen "Zwischenschicht" zwischen DRAM und (NVMe-)Flash, dabei schon länger.

Gen-Z erwähnt SCM ebenfalls. Die Recheneinheiten sollen dabei über ein Memory Semantic Fabric mit Speicher-Pools, Storage und I/O-Systemen kommunizieren – und zwar mit Latenzen, die unter einer Mikrosekunde liegen.

(Bild: Gen-Z Consortium)

Sowohl Micron (QuantX mit 3D XPoint) als auch Samsung (Z-SSD/Z-Flash) haben Konkurrenzprodukte zu Intels 3D XPoint, das bei der kommenden Skylake-Server-Plattform Purley direkt an die Prozessoren angebunden werden soll. Die Kern-Spezifikation für Gen-Z soll noch 2016 erscheinen und sowohl Architektur als auch Protokoll beschreiben. Ob die neue Spezifikation auch "Disintegration" per PCIe oder das SSD-Fabric NVMf berücksichtigt, ist unklar. (ciw)