Microsoft-Prozessor E2 mit EDGE-Architektur und Support für Windows 10 und Linux

Microsoft Research forscht an einer Soft-CPU, die mit Explicit Data Graph Execution eine Variante der Datenfluss-Architektur umsetzt.

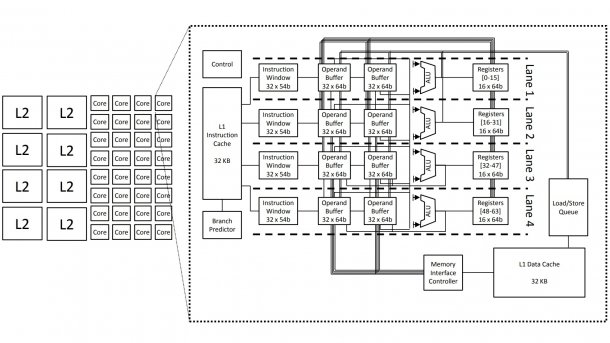

Forschungsprozessor E2 von Microsoft Research mit EDGE-ISA

(Bild: Microsoft Research)

Auf dem 45. International Symposium on Computer Architecture (ISCA 2018) hat Doug Burger von Microsoft Research Forschungsergebnisse zum hauseigenen Soft-Prozessor E2 vorgestellt. Er ist dazu gedacht, sich relativ leicht und effizient in rekonfigurierbaren Logikchips, also in FPGAs implementieren zu lassen. Burger ist auch an Projekten wie Brainwave und Catapult beteiligt, die FPGAs in Azure-Cloud-Rechenzentren für KI-Anwendungen nutzbar machen.

Bevor Doug Burger 2008 zu Microsoft Research wechselte, war er zehn Jahre lang an der Uni Austin tätig und entwickelte den TRIPS-Chip, der eine Variante der Datenfluss-Architektur umsetzte: EDGE steht für Explicit Data Graph Execution. Konzepte von TRIPS flossen in die EDGE-ISA des E2 ein, der auch mit Beteiligung von Qualcomm entwickelt wurde. Gegenüber dem britischen Register stellte eine Microsoft-Sprecherin aber klar, dass eine Fertigung von E2 als diskreter Chip nicht das Ziel sei. Vielmehr sollen die mit E2 gewonnenen Erkenntnisse in weitere Forschungsarbeiten einfließen.

EDGE-ISA

Die EDGE-ISA kann Vektorbefehle Out-of-Order ausführen. Schon 2010 veröffentlichte das E2-Team Methoden, wie sich der E2 dynamisch umkonfigurieren lässt, sodass sich etwa ein Kern in logische Prozessoren aufteilen kann. Dadurch soll sich der E2 rasch an die jeweils anstehenden Rechenaufgaben anpassen lassen, um möglichst viele Operationen parallel auszuführen: High Instruction Level Parallelism (ILP).

Für EDGE sind spezielle Compiler nötig. Diese können jedoch Flaschenhälse der Out-of-Order-Architektur aller gängigen Mikroprozessoren mit von-Neumann-Architektur weiten: Der EDGE-Compiler codiert die Abhängigkeiten zwischen parallel verarbeiteten Daten explizit durch den Befehlssatz (ISA). Deshalb muss die Mikroarchitektur diese Abhängigkeiten nicht erst aufwändig zur Laufzeit auflösen, etwa durch Register Renaming. (ciw)