Intels KI-Beschleuniger NNP-T mit PCIe 4.0 und TSMC-Technik

Intels NNP-T "Spring Crest" soll Nvidias Tesla V100 beim KI-Training schlagen; fürs Inferencing kommt der NNP-I1000 "Spring Hill".

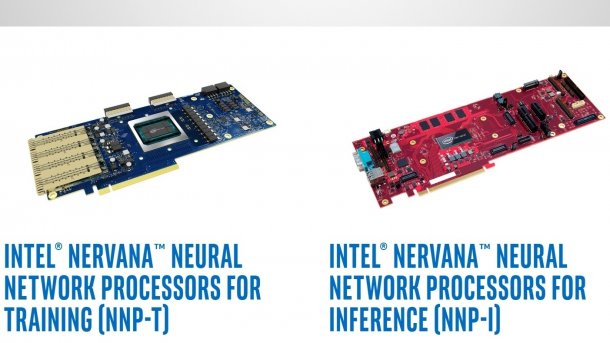

Intel Nervana NNP-T1000 und NNP-I

(Bild: Intel)

119 Billionen Tensor-Operationen pro Sekunde (TOPS): Das verspricht Intel auf der Konferenz Hot Chips HC31 für den kommenden KI-Beschleuniger Spring Crest alias NNP-T1000 alias NNP-L1000. Damit will Intel die Nvidia Tesla V100 schlagen, für die Nvidia 120 TOPS als Maximum nennt. Doch laut Intel soll sich die theoretische KI-Performance beim NNP-T1000 deutlich weiter praktisch ausreizen lassen. Und über ein spezielles Interface mit vier schnellen Ports lassen sich zahlreiche Server mit jeweils mehreren NNP-T eng vernetzen, um die Performance beim Training von KI-Algorithmen noch weiter zu steigern.

Auch zur Anwendung von KI-Algorithmen, dem Inferencing, entwickelt Intel einen dedizierten Beschleuniger namens NNP-I1000 alias Spring Hill. Diesen will Intel mit der hauseigenen 10-nm-Technik selbst produzieren.

NNP-T1000

NNP steht für Nervana Neural Processor: Das Design stammt von der 2016 gekauften Firma Nervana. Daher ist der NNP-T auch nicht für Intels Fertigungstechnik ausgelegt, sondern für die 16-Nanometer-FinFETs von TSMC. Das trägt wohl auch dazu bei, dass der NNP-T bereits PCI Express 4.0 beherrscht, während Intels 14-nm-Chips noch bei PCIe 3.0 festhängen.

Intels KI-Beschleuniger NNP-T1000 und NNP-I (11 Bilder)

(Bild: Intel)

Der NNP-T soll noch 2019 auf den Markt kommen; Intel hatte ihn schon 2018 angekündigt, zwischenzeitlich aber als NNP-L1000. Der Chip vereint 27 Milliarden Transistoren auf 680 Quadratmillimetern Fläche. Er sitzt auf einem 12 Quadratzentimeter großen Interposer gemeinsam mit vier Stapeln mit je 8 GByte ECC-geschütztem HBM-RAM. Insgesamt beträgt die Datentransferrate zum lokalen RAM mehr als 1,2 TByte/s.

Die Leistungsaufnahme liegt laut Intel "typischerweise bei 150 bis 250 Watt". Über 64 schnelle (112 GBit/s) serielle Leitungen, verteilt auf vier Ports, lassen sich bis zu 1024 Servern mit NNP-T1000-Karten ohne zusätzliche Switches koppeln.

Ein NNP-T besitzt 24 Tensor Processing Clusters (TPCs), von denen jeder zwei 32x32-Multiplikatoren für das Datenformat BFloat16 enthält. BFloat16 sollen auch künftige Xeons ab der Generation Cooper Lake verarbeiten. Wann der NNP-T nun konkret auf den Markt kommt, verriet Intel nicht, kündigte aber weitere Benchmark-Ergebnisse vor dem Jahresende an.

NNP-I1000

In einer völlig anderen Performance-Region liegt Spring Hill alias NNP-I1000. Hier steckt schon mehr Intel-Technik drin, konkret die aktuelle 10-nm-Fertigungstechnik und zwei der neuen Sunny-Cove-Rechenkerne, die auch in Ice-Lake-Prozessoren rechnen. Die eigentlichen Deep-Learning-Algorithmen etwa für ein Convolutional Neural Network (CNN) laufen aber auf zwölf Inference Computing Engines (ICEs). Jede davon besitzt wiederum ein sogenanntes Deep Learning Compute Grid sowie eine VLIW-Vektoreinheit auf Basis des DSP Cadence Tensilica Vision P6 (VP6).

Für den gängigen ResNet-50-Benchmark nennt Intel 3600 "Inferences pro Sekunde" bei 10 Watt Leistungsaufnahme des eigentlichen Chips (also ohne sein lokales DDR4-SDRAM) und errechnet daraus eine Effizienz von 4,8 TOPS/Watt. (ciw)