Intels Chipfertigung: Weg von Nanometer, hin zu Angström mit HighNA-EUV

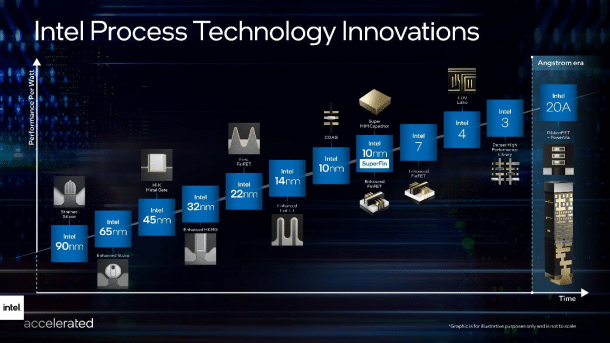

Prozessorhersteller Intel benennt seine Herstellungsprozesse um und gibt Ausblicke auf künftige Produkte von Meteor Lake bis Granite Rapids.

(Bild: Intel)

Bei Intels Chipfertigung lief es in den vergangenen Jahren alles andere als rund. Das größte Sorgenkind war die Fertigung mit 10-Nanometer-Technik, die sich verspätete und erst nach einer Lockerung der Designvorgaben die gewünschten Taktraten jenseits der 4 GHz zuverlässig erreichte.

Diese 10-nm-Technik mit "SuperFin"-Zusatz, welcher die Gates der Transistoren vergrößerte, ist die letzte im klassischen Namensschema. Ab der ehemals "enhanced SuperFin" genannten Generation nutzt Intel eine neue Nomenklatur, sodass der Prozess dann schlicht Intel 7 heißen wird.

Videos by heise

Damit will Intel der Tatsache Rechnung tragen, dass eine einzelne Nanometer-Angabe schon seit vielen Jahren kaum noch adäquat die Strukturgrößen beschreibt und eher ein Marketingbegriff geworden ist. Das hat Intel jahrelang, als man in Sachen Herstellungstechnik weltweit führend war, freilich nicht groß gestört. Auch unabhängige Chip-Experten bestätigten, dass Intels 10-nm-Fertigung in Sachen Transistordichte durchaus mit der 7-nm-Technik des Chipauftragsfertigers TSMC mithalten könne.

(Bild: Intel)

Die neue Zahl soll vielmehr ein Maß sein, welches die Energieeffizienz zur Grundlage hat, wie Intel im Vorfeld des Intel Accelerate-Webcasts mitteilte. Wobei diese Werte schon laut Intel selbst nur lose miteinander zusammenhängen: Intel 7 soll 10 bis 15 Prozent bessere Leistung pro Watt, also Energieeffizienz, haben als 10 nm SuperFin. Intel 4, zuvor als 7-nm-Prozess P1276 bekannt, soll noch einmal 20 Prozent drauflegen und Intel 3 erneut 18 Prozent. Insgesamt wirken die Zahlen eher wie an den Nanometer-basierten Prozessnamen von TSMC und Samsung orientiert.

Produktionsstart Meteor Lake und Granite Rapids

Der Nach-Nachfolger der noch für dieses Jahr erwarteten Alder-Lake-Architektur ist Meteor Lake. Dessen Designpläne sollen bereits an die Fabriken zum Fertigungsstart geschickt worden sein – Intel spricht hier von Tape in, was bei anderen Herstellern Tape out heißt. Je nachdem, ob man das aus Sicht der Designteams (Tape out) oder der Fertigung (Tape in) betrachtet, ist beides richtig. Die Massenproduktion soll indes erst in der zweiten Jahreshälfte 2022 anlaufen, mit Produkten, die eine Spanne von 5 bis 125 Watt Thermal Design Power (TDP) abdecken, ist im Handel daher erst 2023 zu rechnen.

Der Fertigungsprozess Intel 4 ist der erste des Unternehmens, der EUV-Technik einsetzt. Dabei wird die Belichtung mit ultraviolettem Licht mit extrem kurzer Wellenlänge von nur 13,5 nm erzeugt – zuvor nutzte man noch 193 nm lange Lichtwellen. Diese kostenintensive Maßnahme hatte man in der 10-nm-Generation noch vermeiden wollen, woraus wohl einige der Probleme entstanden sind.

Auch die Compute-Tiles der kommenden Granite-Rapids-Chips fürs Rechenzentrum sollen in Intel-4-Technik entstehen.Intel 3 bringt weitere Verbesserungen der Energieeffizienz und zusätzliche Chipschichten, die mit EUV-Belichtung hergestellt werden – auch wenn Intel schon für Intel 4 "Full Use of EUV" angekündigt hat.

Angström-Ära

Größere Neuerungen auf Transistor- wie auf Fertigungsebene gibt es dann mit der ehemals als 2-nm-Technik erforschten, nun Intel 20A genannten Technik. Ein Angström (korrekt: Ångström) entspricht 0,1 Nanometer und wird oft als Einheit für atomare Größenordnungen verwendet. Damit wäre man wieder zurück beim Längenmaß.

(Bild: Intel)

Bei Intels 20A kommen sogenannte RibbonFETs zum Einsatz, Intels Interpretation der Gate-all-around-Technik, bei der der leitende Kanal des Feldeffekttransistors (FET) allseits von der Gate-Elektrode umgeben ist. Ähnliches hatte IBM vor ein paar Jahren als "Nanosheet"-Transistoren angekündigt. Sie sollen bei niedrigerer Spannung schneller schalten und Leckströme gegenüber FinFETs deutlich verringern. TSMC will ähnliche Technik ebenfalls ab der eigenen 2-nm-Generation einsetzen, Samsung ab dem Schritt auf 3 nm.

Ebenfalls neu sind Power Vias, Stromleitungen durch das Silizium bis hin zur Transistorebene, die anders als bisher nicht von oben durch die Transistorschicht, sondern von der Unterseite des Chips ausgehen. Dadurch soll die Signalqualität deutlich verbessert und das Übersprechen zwischen einzelnen Leitungen verringert werden.

Als Nachfolger von Intel 20A wird Intel 18A 2025 an den Start gehen und der erste Intel-Prozess sein, der mit hoher numerischer Blende (High Numerical Aperture) die Chips belichtet. Dafür sind allerdings neue, teure Maschinen nötig, die mehr Platz in den Halbleiterwerken benötigen. Ausrüster ASML will entsprechende Belichtungsmaschinen zusammen mit Partnern ab 2022 testen.

Foveros Direct

Auch die Foveros-Technik wird mit Foveros Direct eine neue Option zu Kopplung mehrerer gestapelter Chips erhalten. War das herkömmliche Foveros noch geeignet, auch Chips verschiedenster Herstellungstechnik durch die sogenannten Mikrobumps miteinander zu verbinden, soll durch die bis zu 10.000 Kupferkontakte pro Quadratmillimeter von Foveros Direct auch einzelne Funktionsblöcke schnell und sicher miteinander verbunden werden – diese sollten dann jedoch aus derselben oder zumindest sehr ähnlicher Fertigung stammen.

(Bild: Intel)

(csp)