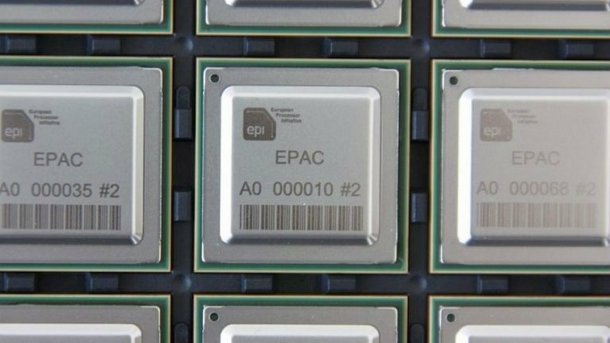

EU-Prozessor: "EPAC"-Testchip mit RISC-V-Beschleunigern

Die European Processor Initiative (EPI) meldet die erfolgreiche Inbetriebnahme von Testchips mit mehreren Beschleunigern, die in der EU entwickelt wurden.

EPI EPAC1.0 mit RISC-V-Beschleunigern

(Bild: EPI)

Die European Processor Initiative (EPI) hat erste Exemplare des von GF (früher Globalfoundries) gefertigten Testchips "EPI EPAC1.0" erfolgreich in Betrieb genommen. Der mit 22-Nanometer-Technik auf Fully-Depleted-SOI-Wafern (22FDX) produzierte Chip vereint sechs Rechenbeschleuniger für unterschiedliche Anwendungen; ein 12-Nanometer-Nachfolger ist in Arbeit.

EPAC steht für European Processor Accelerators. In diesem Teilbereich des EPI-Projekts kooperieren mehrere Firmen und Institute. Vier der EPAC1.0-"Kacheln" (Tiles) sind RISC-V-Vektorprozessoren (VPU). Dabei stammt der RISC-V-Kern von SemiDynamics (Avispado), die Vektorerweiterung hingegen vom Barcelona Supercomputing Center (BSC) und der Uni Zagreb. Den "Home Node" steuert die Uni Chalmers aus Göteborg bei, den L2-Cache das FORTH-Institut aus Kreta.

Videos by heise

(Bild: EPI)

Eine weitere Tile beherbergt den Stencil and Tensor Accelerator (STX) von Fraunhofer IIS, Fraunhofer ITWM und ETH Zürich. Die sechste Tile bildet der Variable Precision Processor (VRP) von CEA LIST (Frankreich).

Alle Tiles sind über ein Network-on-Chip (NoC) verbunden, für das Extoll (Heidelberg) die SERDES-Blöcke zuliefert. Das BSC arbeitet auch an einem offenen Compiler für RISC-V-Vektorerweiterungen. Außerdem ist das BSC am Projekt eProcessor für einen leistungsfähigen RISC-V-Kern mit Out-of-Order-(OOO-)Mikroarchitektur beteiligt.

2022 soll mit Rhea die erste Version des EPI General Purpose Processor (EPI GPP) erscheinen, der 72 ARM-Kerne hat.

(ciw)