Sandisk will 4 TByte Speicher auf eine GPU packen

Sandisk will Beschleuniger mit extrem viel und schnellem Flash-Speicher bestücken. Große KI-Modelle würden so auf eine GPU passen.

(Bild: Sandisk)

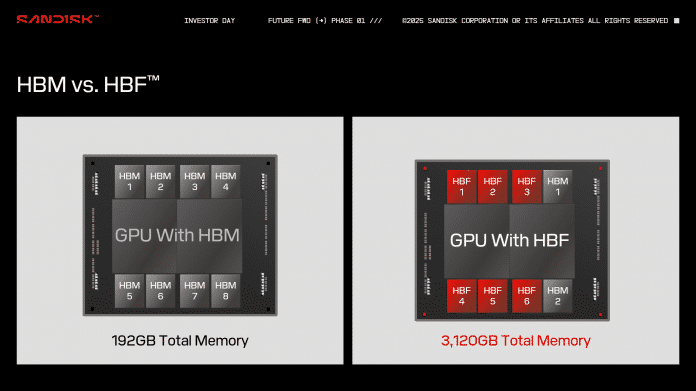

High-Bandwidth Memory (HBM) bekommt Konkurrenz. Der NAND-Flash-Hersteller Sandisk schlägt die Speicherform High-Bandwidth Flash (HBF) für KI-Beschleuniger vor. Anstelle von DRAM-Chips (Dynamic Random Access Memory) tritt namensgebender NAND-Flash, der auf viele parallele Zugriffe optimiert ist.

Der Vorteil von Flash: Er erreicht erhebliche höhere Speicherkapazitäten als DRAM auf gleicher Fläche. Ein HBF-Baustein soll 512 GByte fassen – 21-mal mehr als die aktuelle HBM3e-Generation. Letztere kommt derzeit auf 24 GByte; als Nächstes folgen 48 GByte. HBF soll 8- bis 16-mal so viel Kapazität bei ähnlichen Kosten ermöglichen. Im Umkehrschluss kalkuliert Sandisk also mit höheren Kosten pro HBF-Baustein.

HBF nutzt das gleiche Speicher-Interface wie HBM. Jeder Baustein ist also über 1024 Datenleitungen mit der GPU verbunden. Aufgrund von notwendigen Protokolländerungen ist die Flash-Alternative allerdings nicht eins zu eins für HBM eintauschbar. Die Technik ist mit dieser Anbindung nicht mit früheren Versuchen vergleichbar, SSDs auf eine Grafikkarte zu setzen und per PCI Express anzubinden.

4 TByte Speicher auf aktuellen GPUs

In einer Präsentation referenziert Sandisks angehender Vizepräsident für Speichertechnologie Alper Ilkbahar Nvidias Blackwell-GPUs B100 und B200. Acht HBF-Bausteine ergäben 4 TByte Speicher (4096 GByte). Der Ingenieur betont, dass das für große moderne KI-Sprachmodelle auf einer einzelnen GPU reicht. GPT4 etwa würde mit 1,8 Billionen Parametern etwa 3,6 TByte einnehmen.

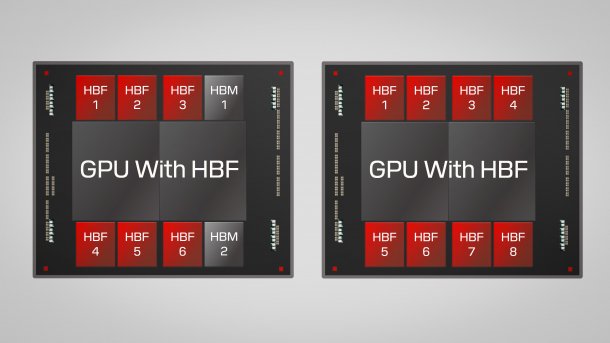

Alternativ könnten Hersteller HBM und HBF mischen. Früher plante Sandisk etwa die Kombination aus sechs HBF- (3072 GByte) mit zwei HBM-Bausteinen (48 GByte). Im DRAM könnten dann Daten wie für den Key-Value-Cache (KV-Cache) von KI-Modellen liegen, die fortlaufend weitergeschrieben werden.

Sandisk High-Bandwidth Flash (HBF) (4 Bilder)

Sandisk

)Ilkbahar führt jetzt aber Neuerungen wie DeepSeeks Cache-Technik Multi-Head Latent Attention (MLA) an, die den Platzbedarf des KV-Caches auf einen Bruchteil schrumpft und weniger Schreibbefehle benötigt. DRAM könnte beim KI-Training so überflüssig werden.

Hohe Leseleistung mit 16 Speicherlagen

HBF wäre insbesondere bei Lesezugriffen flott. Sandisk spricht grob von der gleichen Übertragungsrate wie bei HBM. Acht Bausteine sollten zusammen also mehrere Terabyte pro Sekunde übertragen können, zumindest lesend. Zur Schreibgeschwindigkeit schweigt sich Sandisk aus.

Für die hohe Lesegeschwindigkeit teilt Sandisk jeden NAND-Flash-Chip in unzählige Speicherbereiche auf, die ein Controller parallel anspricht. In einem HBF-Baustein sitzen 16 NAND-Flash-Chips ("16-Hi") auf einer Logiklage für den Controller. Die Verbindung mit einer GPU stellt wie bei HBM ein Silizium-Interposer her. Alternativ könnten Hersteller HBF auf einer GPU stapeln. Denkbar wäre der Einsatz auch bei CPUs oder anderen Prozessortypen.

(Bild: Sandisk)

HBF soll wie HBM ein offener Standard werden, den künftig also auch andere Hersteller fertigen könnten. Die Entwicklung soll 2024 mit Vorschlägen "wichtiger KI-Playern" begonnen haben – in der Industrie scheint es also schon Interesse zu geben. Wann High-Bandwidth Flash marktreif wird, grenzt Sandisk nicht ein.

Für Gaming-Grafikkarten kommt HBF derweil nicht infrage. Schon bei HBM gelten die Kosten für Grafikkarten als zu hoch. Zudem profitieren Spiele von geringen Zugriffslatenzen, die bei DRAM besser sind als bei Flash.

Empfohlener redaktioneller Inhalt

Mit Ihrer Zustimmung wird hier ein externer Preisvergleich (heise Preisvergleich) geladen.

Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit können personenbezogene Daten an Drittplattformen (heise Preisvergleich) übermittelt werden. Mehr dazu in unserer Datenschutzerklärung.

(mma)