Stapel-RAM für (AMD-)Grafikkarten

Künftige Radeon-Karten könnten mit leistungsfähigen SDRAM-Chips bestückt sein, die über 1024 I/O-Kontakten 128 GByte/s pro IC liefern, also insgesamt mehr als 500 GByte/s pro Karte.

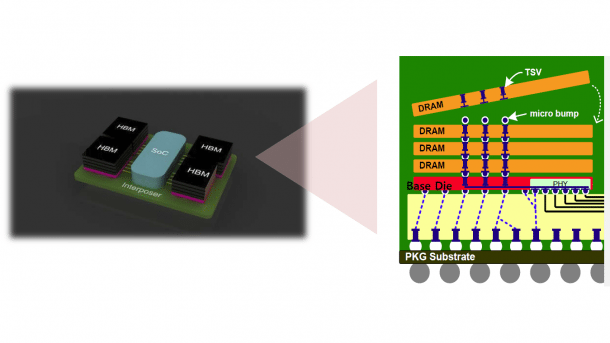

SK Hynix stapelt DRAM-Chips mit vielen Datenleitungen zu High-Bandwidth Memory (HBM).

(Bild: SK Hynix)

High-Bandwidth Memory, kurz HBM, nennt der koreanische Chiphersteller SK Hynix seine neuartigen SDRAM-Bausteine, die bald auf Grafikkarten zum Einsatz kommen könnten – etwa auf der Monster-Karte AMD Radeon R9 390X. Es handelt sich dabei um Die-Stacks mit Through-Silicon Vias (TSVs), die jeweils 1024 Datensignalleitungen besitzen. Bei einer Taktfrequenz von 500 MHz und DDR-Signalisierung überträgt diese "Wide I/O"-(WIO-)Technik 1024 GBit/s, also rund 128 GByte/s.

Bei einem internen HBM-Stapel aus vier einzelnen 2-Gigabit-Dice fasst ein HBM-Chip 1 GByte, eine 4-GByte-Grafikkarte könnnte es auf mehr als 500 GByte/s bringen. Nötig wäre dazu aber auch eine GPU, die über 4096 Datenleitungen verfügt. Zum Vergleich: Die heute bei Grafikkarten üblichen x32-GDDR5-SGRAMs besitzen jeweils 32 Datenleitungen und nur wenige GPUs sind für den Anschluss von mehr als 16 Chips parallel ausgelegt, besitzen also über 512 Datenkontakte. Die Kontakte für Steuerbefehle und Adressen sind dabei nicht mitgerechnet.

High-Bandwidth Memory von SK Hynix (6 Bilder)

HBM und SoC auf Interposer

(Bild: SK Hynix)

Beim HBM von SK Hynix sind für Adressen und Befehle ebenfalls zusätzliche Leitungen vorgesehen; dafür ist im HBM-Bauelement als unterste Funktionslage ein Controller integiert, der die zunächst vier und in späteren Generationen auch mehr DRAM-Dice ansteuert. Anders als bei Microns Hybrid Memory Cube (HMC) von Micron führen die Datenleitungen aber direkt zu den einzelnen DRAM-Dice. Beim HMC gibt es ein Logik-Die, welches die Datensignale auf einen externen Link umsetzt: So sind längere Leitungspfade möglich und Zusatzfunktionen wie Fehlerkorrektur auf dem Speicherlink, außerdem braucht man weniger Signalleitungen – handelt sich aber möglicherweise längere Latenzen ein.

GPU-HBM-Interposer

Soweit derzeit erkennbar, sind die HBM-Chips von SK Hynix nicht dazu gedacht, direkt auf dem GPU-Chip angepracht zu werden, weder als Package-on-Package-(PoP-)Stapel, noch als interner Die-Stack. Vielmehr sollen die HBM-Chips wie herkömmliche DRAM-Chips auf Grafikkarten dicht neben der GPU sitzen. SK Hynix erwähnt auch die Möglichkeit, die GPU und die HBM-Chips zusammen auf einem kleinen "Interposer" unterzubringen, also einer Trägerplatine, die dann als Ganzes auf die Grafikkarte gelötet wird.

Eine komplette öffentliche Dokumentation fehlt, weshalb sich auch nicht sagen lässt, ob sich mehr als ein HBM-Chip an eine Datenleitung anschließen lässt – für eine Karte mit 8 GByte wären dann vier 2-GByte-HBM-Bauelemente nötig und man könnte nicht etwa acht 1-GByte-Versionen nehmen. Ob die Grafikkarten-Hersteller die Möglichkeit haben werden, GPU und HBM-Chips selbst zu kombinieren, ist offen; möglicherweise liefert AMD GPU und RAM jeweils im Paket auf dem Interposer.

Laut SK-Hynix-Webseite sind derzeit zwei HBM-Chips mit je 1 GByte lieferbar, und zwar mit entweder 0,8 oder 1 GBit/s (H5VR8GESM4R-25C/-20C). Es handelt sich um "4Hi-Stacks", also Stapel mit vier DRAM-Dice.

Xeon Phi mit Micron HMC?

Auf dem Intel-Entwicklerforum im September zeigte SK Hynix eine Präsentation unter anderem zu HBM; allerdings will Intel beim 2015 erwarteten Xeon-Phi-Rechenbeschleuniger Knights Landing angeblich auf Microns HMC setzen. Nvidia plant Pascal mit nicht näher beschriebenen DRAM-Stacks für 2016. Laut Chipworks setzt Sony in der Playstation Vita schon seit einigen Jahren aufgestapelte Wide-I/O-DRAMs mit 1024 Datenleitungen ein. (ciw)