Netzwerkprozessor mit hundert 64-Bit-Prozessorkernen

Die von EZchip gekaufte Firma Tilera kündigt den Tile-Mx100 mit 100 Cortex-A53-Cores an, also mit ARM-Technik statt den bisherigen VLIW-Kernen.

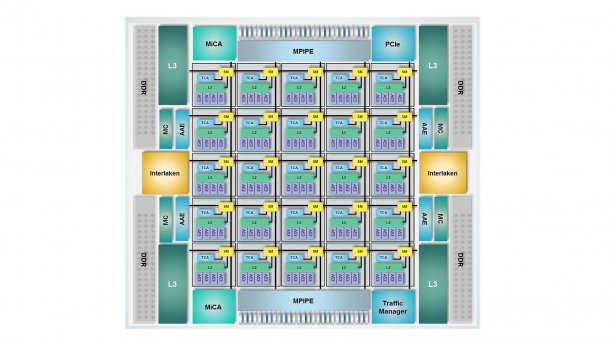

Der Tile-MX100 der EZchip-Tochter Tilera vereint 100 Cortex-A53.

(Bild: EZchip)

Für Netzwerkgeräte wie Router, die große Datenströme mit geringer Latenz verarbeiten müssen, entwickeln die israelische Firma EZchip und deren 2014 zugekaufte Tochter Tilera Multi-Core-Prozessoren mit sehr vielen Kernen. Vorläufiger Spitzenreiter soll der Tile-Mx100 werden, der 100 Cortex-A53-Kerne in 25 Quad-Core-Gruppen auf einem Chip vereint. Er wird allerdings wohl erst 2017 in serienreifen Geräten zum Einsatz kommen, Muster sind für die zweite Hälfte kommenden Jahres geplant. EZchip will eines Tages auch 64- und 36-Kern-Varianten liefern.

Für ihre bisherigen Multi-Core-Chips mit bis zu 72 Kernen namens Tile-Gx setzte Tilera auf eine hauseigene VLIW-Mikroarchitektur. Nun kommt der ARM Cortex-A53 zum Einsatz. Wie EZchip betont, liegt das besondere Know-how von Tilera aber eher in der effizienten Verknüpfung vieler CPU-Cores auf einem eigenen Chip, nämlich mit einem Mesh-Netzwerk. Der hierarchische Traffic-Manager verwaltet Aufgaben in 256.000 Queues. Hinzu kommen Kryptobeschleuniger (MICA: Multistream iMesh Crypto Accelerator). Die Speicher-Controller steuern bis zu 1 TByte DDR4-SDRAM mit ECC als lokalen Speicher an. Der Tile-Mx100 kann etwa auf PCIe-3.0-Karten zum Einsatz kommen.

Zur Fertigungstechnik und zur Leistungsaufnahme des Tile-Mx100 äußert sich EZchip nicht; für den TILEncore-Gx72 Intelligent Adapter mit dem 72-kernigen Tile-Gx72 und 32 GByte DDR3-1600-RAM nennt EZchip aber eine "Typical Power" von 95 Watt. (ciw)