Flash Memory Summit: Neue Stapeltechnik für schnellere und sparsamere SSD

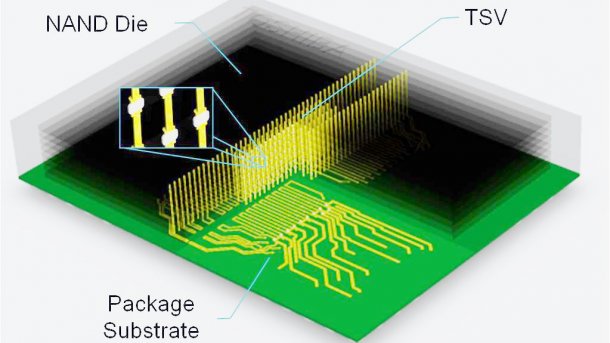

Senkrechte Bohrungen und Durchkontaktierungen direkt durch das Silizium an Stelle von Drähten am Rand: Mit Through Silicon Vias baut Toshiba besonders schnelle und sparsame NAND-Flash-Chips.

Auf dem Flash Memory Summit im kalifornischen Santa Clara hat Toshiba erstmals gestapelte Flash-Chips mit Through Silicon Vias (TSV) gezeigt. Stapel aus mehreren Silizium-Dies mit NAND-Zellen gibt es schon länger. Doch bisher wurden die Silizium-Dies nur aufeinander geklebt und am Rand mit hauchdünnen Drähten (Wire Bonding) verbunden. Das begrenzt die Zahl der möglichen Kontakte und den Wärmetransport. Bei TSV verbinden unterdessen über die ganze Die-Fläche verteilte senkrechte Durchkontaktierungen die einzelnen Chip-Lagen miteinander und über das "Package Substrat" und dessen Lotkugeln letztlich mit der Außenwelt.

Das ist zwar eine Herausforderung für die Herstellung, kommt aber der Performance zu Gute. So sollen Toshibas neue Chips mit ihren 8 bis 16 Lagen bis zu 1,2 GBit/s liefern – mehr als alle anderen Chips bei vergleichbar niedriger Kernspannung. Außerdem soll die Leistungsaufnahme durch TSV um bis zu 50 Prozent sinken und die Gehäusefläche abnehmen. Die neuen Chips messen nur 14 mm × 18 mm.

Optimiert sind die neuen Chips für niedrige Latenz, hohe Bandbreite und viele I/O-Operationen pro Watt. Als Einsatzgebiete nennt Toshiba erst einmal High-End Enterprise SSDs. Termine für konkrete Produkte mit den neuen TSV-Chips stehen noch nicht fest. Wohl aber die Kapazitäten der Chips: Ein Stapel aus 8 Lagen speichert 128 GBit und einer aus 16 Lagen 256 GBit. (bbe)