Soft Machines gegen Cortex 72, Apple A9x und Skylake

Shasta, Shasta+ und Tahoe, so lauten die Namen der nächsten VISC-Prozessoren von Soft Machines. Zumindest in den Simulationen lassen sie bei Single-Thread-Benchmarks A9x, Cortex A72 und Core i5 6200U (Skylake) weit hinter sich.

(Bild: Soft Machines)

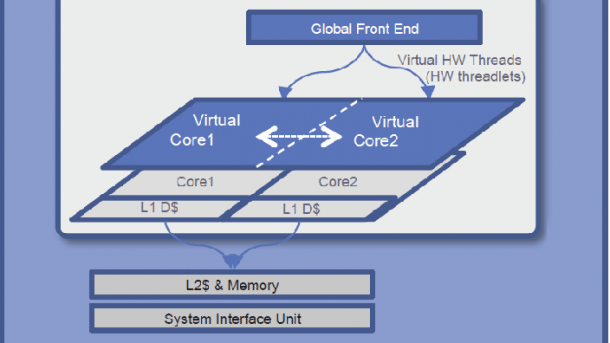

Das kalifornische Startup Soft Machines hat eine neue Roadmap der nächsten Prozessorgenerationen Shasta und Tahoe mit Performance- und Energieergebnissen von den ersten Prototypen und aus dem Simulator vorgelegt, die, falls sich das hardwaremäßig auch alles so realisieren lässt, Apples A9x, ARM Cortex A72 und Intels Skylake (i5 6200U) ziemlich alt aussehen lassen – zumindest bei Single Thread Performance. Denn dafür ist die VISC-Technik der Prozessoren optimiert, bei denen mit einer Art inversem Hyperthreading mehrere physische Prozessoren an einem Thread arbeiten und so bis zu 10 Instruktionen per Takt ausführen können. Im Schnitt, so Soft Maschine CEO Mohammed Abdallah zu heise online, liegen sie bei einem IPC-Wert von 4 bis 6, was mehr als doppelt so hoch ist, wie bei den üblichen Out-of-Order arbeitenden Prozessoren.

Als Benchmark kommt bei Soft Machines SPEC CPU2006 zum Einsatz, und zwar das geometrische Mittel der SPECfp- und SPECint-Komponenten. Diese hat Soft Machines mit gcc 4.9 beziehungsweise auf dem iPhone/Ipad mit Clang 7 zum Laufen gebracht. Für die eigenen VISC-Prozessoren braucht man keinen speziellen Compiler, die laufen mit den Binärdateien einer vorgegebenen ISA, im Moment mit den ARMv8-Code des A72, weitere Instruktionssätze sind in Vorbereitung.

(Bild: Soft Machines )

Für den Energieverbrauch hat Soft Machines allerdings eine etwas undurchsichtige Normierung gemäß "industry scaling metrics" durchgeführt, und zwar normiert auf einen 16-nm-Prozess und eine L2-Cachegröße von 1 bzw. 2 MByte. Die Korrekturen betragen letztlich aber nur wenige Prozent versicherte Mohammed Abdallah, liegen deutlich unter 10 Prozent. Und 10 Prozent können die weit abgeschlagenen anderen Vertreter auch nicht mehr retten. Je nach Performancebereich werden sie nach den Ergebnissen von Soft Machines in der Energieeffizienz, gemessen in Watt pro SPEC2006, um Faktor 2-3 bis hinauf zu Faktor 7 abgehängt. Gibt man einen festen Energieverbrauch vor, so kommen die Shasta-Prozessoren auf eine um Faktor 1,6 bis 2 höhere Performance, die für später geplanten Tahoe-Prozessoren sollen etwa bei angenommenen 3 Watt um bis zu Faktor 2,5 schneller sein.

(Bild: Soft Machines)

Lizenznehmer sollen ab Mitte des Jahres die RTL-Designdateien für den ersten kommerziellen Prozessor Shasta erhalten können, vorbereitet für den 16-nm-Prozess von TSMC. Shasta soll es daneben auch als SMP-Version mit zwei zusammengeschalteten Dual-Cores geben. Fürs dritte Quartal ist dann das Tape-out der SoC-Version namens Mojave geplant, das zahlreiche Zusatzhardware bietet.

Optimistisch geht Soft Machines fürs nächste Jahr von einem 10-nm-Prozess aus. Der dafür geplante Shasta+ soll aber nicht nur ein Shrink auf den neuen Prozess darstellen, sondern auch Architekturverbesserungen enthalten, die IPC etwa um 15 Prozent steigern. Das zugehörige SoC heißt Tabernas. Mit vier physischen Kernen soll dann 2018 der Tahoe und das SoC Ordos hinzukommen. (as)