IBM und Fertigungspartner zeigen 5-Nanometer-Transistor mit "Gate All Around"

IBM meldet die erfolgreiche Fertigung erster Chip-Muster mit GAA-FETs mit 5-nm-Strukturen; bei diesen Nanosheet-Transistoren kam auch EUV-Lithografie zum Einsatz.

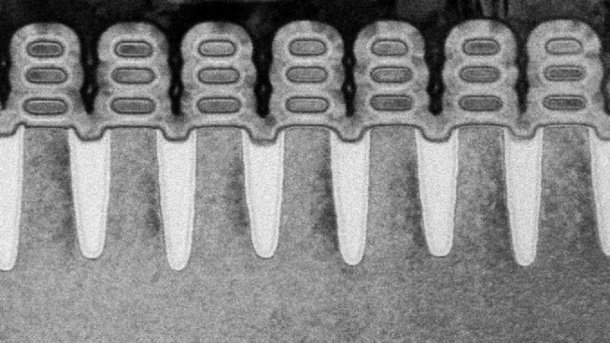

Nanosheet-Transistoren (GAA-FETs) aus Silizium

(Bild: IBM)

IBM und die Fertigungspartner Globalfoundries und Samsung sehen den Weg zur 5-Nanometer-Technik geebnet: Auf dem VLSI Symposium in Kyoto präsentieren IBM-Entwickler Details der ersten GAA-FET-Chips mit 5-nm-Strukturen.

Im Vergleich zu Fin-FETs soll die "Gate All-Around"-(GAA-)Technik bei kleineren Strukturen höhere Leistungen ermöglichen. Der leitende Kanal des Feldeffekttransistors (FET) ist bei GAA-FETs allseits von der Gate-Elektrode umgeben.

IBM spricht nicht von GAA-FETs, sondern von Nanosheets (Nanoblättern): Die FET-Struktur besteht aus mehreren dünnen Schichten. Zur Herstellung der feinsten Strukturen verwendet IBM dabei Extrem-Ultraviolett-(EUV-)Lithografie, genau wie bei der 7-nm-FinFET-Fertigungstechnik der IBM-Fertigungsallianz, zu der Globalfoundries und Samsung gehören.

Die 5-nm-Nanosheet-Technik wurde im Rahmen eines Forschungsprojekts am NanoTech-Complex der Uni Albany entwickelt.

7 nm 2018, 5 nm wann?

IBM nennt keine Termine für die Serienfertigung erster 5-nm-GAAFET-Chips. Globalfoundries will 2018 die ersten 7-nm-Chips produzieren, beispielsweise für AMD. Die 5-nm-Technik dürfte dann frühestens zwei Jahre später debütieren, also beispielsweise 2020.

Samsung hatte kürzlich eine Roadmap bis hin zu 4-nm-Chips skizziert. Dabei sollen 6-nm-Strukturen (6LPP) durch eine Verbesserung der 7-nm-Technik möglich werden. Bei 5LPP wiederum will Samsung einige Komponenten der 4LPP-Fertigung früher anbieten: 4LPP soll mit einem Samsung-eigenen Typ des GAAFET möglich sein, dem MBCFET (Multi Bridge Channel FET). (ciw)