Hot Chips: EMIB statt Interposer für Multi-Chip-Packages

Intel hat Details seiner Interposer-Alternative EMIB vorgestellt, die derzeit bereits beim hauseigenen FPGA-Flaggschiff Stratix 10 zum Einsatz kommt.

(Bild: Intel)

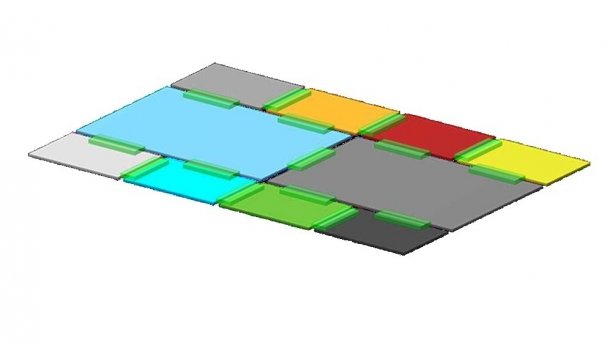

Um mehrere separate Dice auf einer Trägerplatine, dem sogenannten Package, zu vereinen, kommt üblicherweise ein Interposer zum Einsatz, der die einzelnen Chips miteinander verbindet. Intels FPGA-Abteilung geht bei ihrem aktuellen Highend-Modell Stratix 10 einen anderen Weg: Hier befindet sich nur ein kleiner Verbinder zwischen je zwei Dice. Die restliche Chipfläche liegt wie bei Single-Die-Packages auf dem eigentlichen Trägermaterial auf. Dieses EMIB (Embedded Multi-Die Interconnect Bridge) genannte Verfahren soll kostengünstiger als vollflächig ins Substrat eingearbeitete Interposer sein.

EMIB sieht zwei Arten von Schnittstellen vor. UIB ist für "dumme" Zusatzbausteine wie etwa HBM-Speicherstapel gedacht, die als Slave angesprochen werden. Für komplexere Bausteine mit eigenen Taktdomänen ist die flexiblere und leistungsfähigere AIB gedacht.

Um die EMIB-Verbinder im Substrat möglichst klein zu halten, kommt ein komprimiertes BGA-Raster zum Einsatz: Statt mehr als 100 µm beträgt der Abstand derzeit 55 µm. In der nächsten Generation soll er auf 35 µm gesenkt werden

Intel EMIB statt Interposer (5 Bilder)

Vorteile

Der erstmalige Einsatz bei einem FPGA-Chip kommt nicht von ungefähr, denn üblicherweise gehören zu einem solchen außer dem Gatter-Array an sich auch DACs, Funkmodule oder analoge Bausteine. Genau diese Kombination ist allerdings alles andere als optimal: Die Zusatzkomponenten brauchen eine möglichst rauschfreie Umgebung, während das Gatter-Array bauartbedingt viel Rauschen erzeugt. Lagert man die jeweiligen Teile in eigene Dice aus, hat man das Problem sehr einfach gelöst.

Hinzu kommt, dass sich nicht jeder Fertigungsprozess für jede Art von Chip eignet: Analoge Schaltungen oder Treiberstufen mit höheren Spannungen werden üblicherweise in deutlich älteren Prozessen gefertigt als Logik. Bei EMIB kommt als weiterer Vorteil hinzu, dass alle Leitungen, die nach außen gehen, direkt durch das Substrat geführt werden können – bei Interposern ein kritisch Aspekt, vor allem bei den Spannungsleveln von I/O-Pins.

Unabhängig von der konkreten Realisierung modularisiert ein Multi-Chip-Package die Entwicklung. Peripheriebausteine lassen sich in Kombination mit mehreren Haupt-Chips verwenden, während letztere mit neuer Peripherie auch für andere Einsatzzwecke fit gemacht werden können.

Nicht zuletzt lassen sich Fertigungskosten drücken und die Ausbeute erhöhen, wenn man mehrere kleinere Dice zu einem Verbund zusammenfasst. AMD demonstriert dies bereits beim Sever-Prozessor Epyc, der vier Achtkerner auf einer Trägerplatine vereint. Man darf also gespannt sein, wie Intel künftig über monolithische Riesenchips wie Skylake-SP mit bis zu 28 CPU-Kernen nachdenkt... (mue)