DDR5-Speichermodule mit eigener Stromversorgung für Server

Kommende Registered DIMMs mit DDR5-SDRAM für Server sollen eigene Spannungswandler bekommen, was einige Vorteile vereint.

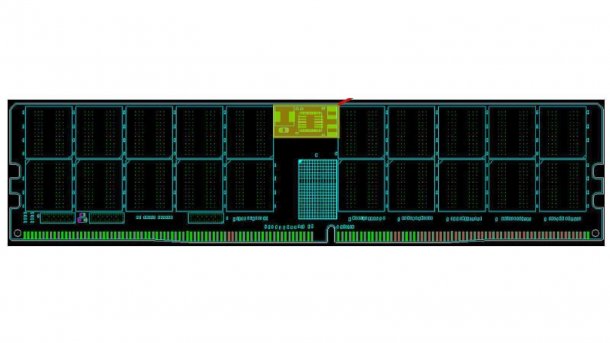

DDR5-RDIMM mit PMIC: Der Spannungswandler sitzt bei diesem Intel-Vorschlag oben in der Mitte über dem Buffer-Chip.

(Bild: IDT/Intel)

Das Komitee JC-42 im Industriegremium JEDEC arbeitet seit einiger Zeit an der Spezifikation von DDR5-SDRAM, welches in einigen Jahren den aktuellen DDR4-Hauptspeicher ablösen soll. DDR5-SDRAM soll bei ähnlicher Leistungsaufnahme vor allem deutlich höhere Transferraten ermöglichen, so wie es bei jedem DDR-RAM-Generationswechsel üblich ist. Für Server kommen mit DDR5-RAM aber noch weitere Neuerungen hinzu, wie eine Präsentation der Firma IDT auf dem JEDC Server Forum zeigt.

Demnach arbeitet die Firma IDT, die beispielsweise Register-/Buffer-Chips für Registered DIMMs (RDIMMs) und Load-Reduced DIMMs (LRDIMMs) liefert, an der Spezifikation eines Power Management IC (PMIC) für DDR5-RDIMMs mit. Dieser PMIC soll die DRAM-Chips auf dem Speichermodul mit Strom versorgen. Laut der Präsentation versorgt das Mainboard das DDR5-RDIMM mit 12 Volt (10,8 bis 13,8 Volt) und der PMIC erzeugt daraus 1,0 Volt für die DDR5-SDRAMs. Außerdem stellt der PMIC noch die Referenzspannung VDDQ mit 1,1 Volt für die Datensignale bereit sowie 1,8 Volt als Versorgungsspannung für das SPD-EEPROM, den Temperatursensor (TS) und den Pufferchip, genannt Register Clock Driver (RCD).

Weniger Platz und Kosten

DDR5-RDRAMs sollen mehrere Probleme bei der RAM-Stromversorgung auf Server-Mainboards lösen. So ist der Platzbedarf für die RAM-Spannungswandler (Voltage Regulator Module, VRM) relativ hoch, wenn viele DIMM-Slots vorhanden sind – auf Serverboards können es 16 bis 32 DIMM-Slots sein. Diese RAM-VRMs müssen relativ hohe Spitzenströme stabil liefern, weil beispielsweise ein einzelnes 32-GByte-DDR4-RDIMM fast 5 Ampere ziehen kann. Laut IDT muss die Spannung dabei auf 3 Prozent genau bleiben, was bei stark schwankenden Strömen eine recht aufwendige Regelung erfordert.

Ein RAM-VRM ist also nicht ganz billig und benötigt Platz. Doch in den meisten Servern wird nur die Hälfte der DIMM-Slots überhaupt belegt, sagt IDT. Wandert das VRM aufs DIMM, können Mainboards etwas billiger ausfallen. Auch die Kühlung ließe sich verbessern: Bei Serverboards für Rack-Gehäuse sind die DIMM-Slots typischerweise "in Windrichtung" orientiert.

16-Bit-ECC und I3C

Nebenbei enthüllt die IDT-Präsentation noch einige Details zu DDR5-SDRAM. Demnach beträgt die Betriebsspannung der SDRAM-Chips bei DDR5 noch 1,0 Volt; bei DDR4 sind es 1,2 Volt, bei DDR3L 1,35 und bei DDR3 1,5 Volt.

(Bild: MIPI Alliance)

Der Speicherbus für die DDR5-ECC-RDIMMs wird 80 Bit "breit" sein; bis DDR4 sind 72 Bit üblich, von denen 64 Bit für Nutzdaten dienen und 8 Bit für redundante Daten für den Error Correction Code (ECC). Mit DDR5 kommt also demnach 16-Bit-ECC, was erweiterte Optionen zur Fehlerkorrektur bringt.

Für die Kommunikation zwischen Mainboard und SPD-EEPROM und Temperatursensor kommt bei DDR5 das 2016 von der MIPI verabschiedete I3C-Verfahren zum Einsatz, der Nachfolger von I2C.

I3C steht für Improved Inter-Integrated Circuits. I3C bleibt abwärtskompatibel zu I2C und kann teilweise auch SPI ersetzen; außer höheren Transferraten im Vergleich zu I2C bringt es auch die Möglichkeit, Interrupts ohne Zusatzleitungen zu übertragen. (ciw)