RISC-V mit 64-Bit-Architektur als IP-Core lieferbar

Die Firma SiFive liefert Verilog-Pakete für Systems-on-Chip mit vier CPU-Kernen vom Typ RISC-V RV64GC; ein Entwicklerboard mit diesem U54-MC Coreplex aus der 28-nm-Fertigung kommt 2018.

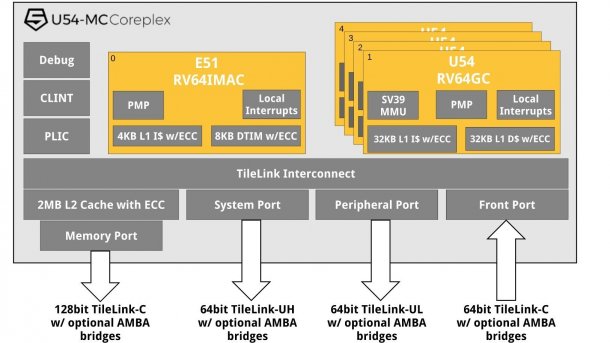

SiFive U54-MC Coreplex mit RISC-V RV64GC (U54) und RV64IMAC (E51)

(Bild: SiFive)

Von der freien Prozessorarchitektur RISC-V gibt es nun auch die 64-Bit-Version RV64GC als geistiges Eigentum (Intellectual Property/IP) in der Hardware-Beschreibungssprache Verilog. Damit können Chip-Entwickler Systems-on-Chip mit dem SiFive U54-MC Coreplex entwerfen.

Das Chip-Design enthält vier RISC-V RV64GC mit M+S+U-Modus namens U54, die bei Fertigung mit 28-Nanometer-Technik (28nm HPC) mehr als 1,5 GHz erreichen sollen. Ein separater E51-Kern (RV64IMAC) dient als "Monitor Core".

Jeder der "Applikationskerne" U54 besitzt je 32 KByte L1-Cache für Daten (L1D) und Befehle (L1I), hinzu kommen 2 MByte kohärenter L2-Cache; alle Caches sind ECC-geschützt. Der U54 hat eine In-Order-Pipeline mit fünf Stufen. Der Speicher-Controller SV39 MMU unterstützt Virtual Memory mit 38 Adressbits.

Entwicklerboard 2018

Für das erste Quartal 2018 verspricht SiFive ein Entwicklerboard mit einer "Freedom Unleashed"-Implementierung des U54-MC Coreplex. Bisher gibt es dazu keine weiteren Informationen, etwa zu Preis, Schnittstellen und RAM-Ausstattung.

Das bisherige Developer Kit mit FPGA für den Freedom U500 mit dem U5 Coreplex kostet über 3500 US-Dollar. Rund 100 US-Dollar kostet das Freedom E300 Arty FPGA Dev Kit, das den E51 mit 65 MHz ausführen kann.

Die 32-Bit-RISC-V-Implementierung E31 Coreplex steckt im SoC Freedom E310, das wiederum auf dem 60 bis 70 Euro teuren Entwicklerboard HiFive1 sitzt sowie auf dem Arduino Cinque. (ciw)