Kompletter Mainboard-Schaltplan für Hardware-Nerds

Früher fand man auf den Intel-Servern noch komplette Mainboard-Schaltpläne. Das ist lange vorbei, doch beim Open Compute Project (OCP) wird man noch fündig.

(Bild: Open Compute Project (OCP), Microsoft)

Wer tief genug gräbt, findet auf den Webseiten des Open Compute Project (OCP) den kompletten Schaltplan eines Cloud-Server-Mainboards mit zwei Intel Xeon Scalable Performance (Xeon-SP, Skylake-SP). Microsoft hat das Mainboard im Rahmen des Project Olympus für Azure-Server entworfen und veröffentlich diese Baupläne im Rahmen des OCP. Die Pläne und die komplette Komponentenliste (Bill of Material, BOM) sind in der ZIP-Datei "Project_Olympus_Intel_XSP_Collateral.zip" im Unterverzeichnis EE_Collateral zu finden.

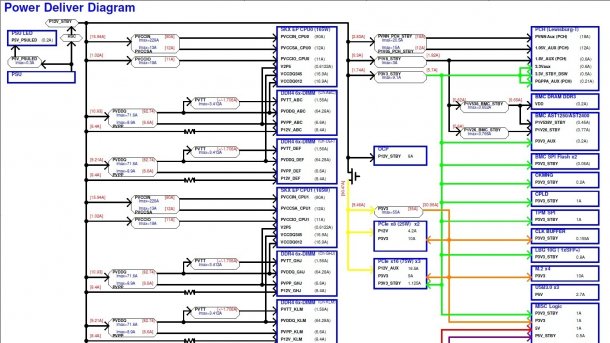

Der Schaltplan "Project_Olympus_Intel_XSP_Schematics_20171016.pdf" zeigt auf 288 Seiten die Verdrahtung und die Mainboard-Komponenten. Spannend ist beispielsweise schon die Stromversorgung auf Seite 7: Dass moderne Prozessoren wegen der extrem niedrigen Betriebsspannungen starke Ströme ziehen, ist bekannt - in diesem Falls sind es bis zu 228 A pro CPU. Doch auch das DDR4-DRAM ist kein Kostverächter: Die Spannung ebträgt nur 1,2 Volt und auf einem 128-GByte-LRDIMM sitzen bis zu 72 Dual-Die-SDRAM-Chips (Octal-Rank). Pro sechs DIMM-Slots - insgesamt sind 24 vorhanden - sieht der Stromlaufplan 72 A auf der VDDQ-Schiene vor.

(Bild: Molex)

Spannend fand ich auch die Boot-Sequenz-Diagramme ab Seite 8 - moderne Boards sind ganz schön komplex.

Der Schaltplan verrät auch die Belegungen vieler gängiger Steckverbinder. Noch ziemlich neu auf Serverboards ist OCuLink, ein Anschluss für PCIe-Kabelverbindungen zwischen Mainboard und NVMe-SSD-Backplane. Hierbei verwendet man das Nano-Pitch-I/O-System von Molex in der Version mit 80 Kontakten. (ciw) (ciw)