Chip-Fertigungstechnik bei TSMC: 5 Nanometer schon 2020, 3 Nanometer ab 2022

TSMC macht Dampf bei der Halbleiterfertigung: 5-nm-Technik läufts bereits versuchsweise und soll in einem Jahr in Serie gehen.

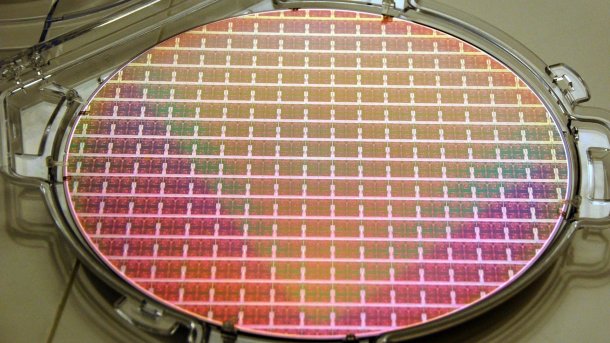

Ein 300-mm-Wafer mit belichteten Siliziumchips.

(Bild: c't/Christof Windeck)

Sechs neue Fertigungsprozesse entwickelt der weltweit größte Chip-Auftragsfertiger TSMC zurzeit. Unmittelbar vor der Tür stehen zwei neue 7-nm-Ableger, von denen AMD einen für seine kommenden Zen-3-Prozessoren nächstes Jahr verwenden möchte.

Darauf folgen 5- und 3-nm-Prozesse, bei denen TSMC häufiger Lithografie mit extrem ultraviolettem Licht einsetzt.

Drei 7-nm-Prozesse von TSMC

Aktuell lässt AMD seine Zen-2-Chiplets, unter anderem für seine Ryzen-3000-Prozessoren, und die Navi-GPUs für die Radeon RX 5700 (XT) im N7-Prozess mit klassischer Immersionslithografie fertigen. Bei N7+ belichtet TSMC die ersten Chiplayer mit extrem ultraviolettem (EUV-)Licht, um Fertigungsschritte zu sparen – Stichwort: Mehrfachbelichtung, zu Englisch Multi-Patterning – und die elektrischen Eigenschaften zu verbessern.

TSMC spricht im Vergleich zu N7 von einer 20 Prozent höheren Packdichte. Die Performance soll bei gleicher Leistungsaufnahme um zehn Prozent steigen oder die Leistungsaufnahme bei gleicher Performance um 15 Prozent sinken. Performance meint hier: Grundsätzlich erlauben feinere Fertigungsprozesse kürzere Transistorschaltzeiten, sofern das Chipdesign darauf ausgelegt ist.

Die Serienproduktion von N7+ hat im zweiten Quartal 2019 begonnen. AMD wird sich mit der Nutzung noch bis 2020 Zeit lassen.

Daneben bietet TSMC jetzt eine "Performance-enhanced"-Version von N7, kurz N7P, an, wie die Webseite Wikichips berichtet. N7-Designs lassen sich dank identischer Design-Regeln zu N7P portieren und sollen entweder sieben Prozent schneller oder zehn Prozent sparsamer werden. AMD könnte in Zukunft zum Beispiel einen Navi-Refresh analog zu Polaris 30 in 12 statt 14 nm (Radeon RX 590 vs. RX 580) bringen.

N6 soll ebenfalls die gleichen Design-Regeln wie N7 aufweisen, aber trotzdem EUV-Technik integrieren. Da N6 nach dem ersten 5-nm-Prozess, N5, fertiggestellt wird, ist er für AMD und Nvidia weniger interessant.

5 nm in Risikoproduktion

Bei N5 weitet TSMC die Nutzung der EUV-Lithografie aus. Gegenüber dem aktuellen N7 (nicht N7+) fällt die Packdichte um 80 Prozent höher aus. Die Performance soll bei gleicher Leistungsaufnahme um 15 Prozent steigen oder die Leistungsaufnahme bei gleicher Performance um 30 Prozent sinken. Bei einer HPC-Version sieht TSMC eine 25 Prozent höhere Leistung im Tausch gegen etwas Packdichte vor.

Die sogenannte Risikoproduktion von N5 hat bereits zum Jahresanfang begonnen. In der ersten Jahreshälfte 2020 möchte TSMC die Fertigung hochfahren – und das schneller als seinerzeit bei N7. Wikichip geht davon aus, dass die Taiwaner die ersten mit einem 5-nm-Prozess sein werden und dann vor Intel und Samsung eine volle Fertigungsstufe Vorsprung haben.

Auch von N5 soll es eine optimierte Performance-Version geben, N5P genannt. Sieben Prozent mehr Performance oder eine um 15 Prozent reduzierte Leistungsaufnahme stehen auf dem Plan.

3 nm macht Fortschritte

Die Entwicklung von N3 soll gut voranschreiten. Gegen 2022 könnte die Fertigung mit 3-nm-Strukturbreiten anlaufen. Leistungsdaten werden in so einem frühen Stadium nicht genannt. TSMC scheint noch einmal auf bewährte FinFET-Transistoren zu setzen, bevor die winzigen Strukturen einen Wechsel auf eine Alternative wie Gate-All-Around-(GAA-)Designs erfordern.

(mma)