AMD Renoir: Neue Hinweise auf 7-nm-Mobilprozessoren mit Vega-GPU

AMD hält sich zu den APUs mit dem Codenamen Renoir äußerst bedeckt. Umso spannender sind die inoffiziellen Informationen, unter anderem durch Linux-Patches.

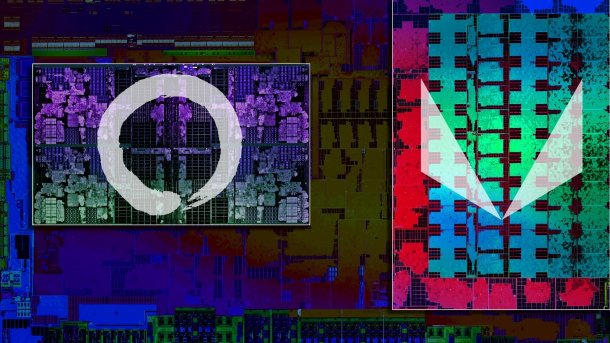

Nachbearbeiteter Die-Shot eines Picasso-Kombiprozessors.

(Bild: AMD)

Voraussichtlich ab 2020 will AMD neue Kombiprozessoren mit dem Codenamen Renoir anbieten. Sie lösen die aktuellen Picasso-APUs ab, die im Desktop als Ryzen 3000G und in Notebooks als Ryzen 3000U/H vier CPU-Kerne des Typs Zen+ mit einer bis zu 704 Shader-Kernen starken Vega-GPU vereinen.

Bleibt AMD seinem Veröffentlichungsrhythmus treu, sollte die Vorstellung von Renoir für Notebooks zur CES im Januar 2020 als Ryzen 4000U/H erfolgen. Der Desktop-PC ist mit Ryzen 4000G traditionell ein gutes halbes Jahr später zusammen mit den neuen Zen-3-CPUs dran.

Die Verwendung von TSMCs 7-nm-Prozess N7 gilt als gesichert, ebenso der Einsatz von Zen-2-Kernen.

AMD hält sich bedeckt, Linux gibt erste Auskünfte

AMD-CEO Lisa Su bestätigte im Interview mit der Webseite Anandtech den Codenamen Renoir und dass die Entwicklung gut vorangehe. Mehr Details wollte sie sich nicht entlocken lassen.

Im Hintergrund arbeitet AMD bereits an den Treibern für die kommenden Kombiprozessoren. In Linux-Patches tauchen die ersten Referenzen zu Renoir auf, die Rückschlüsse auf die Architektur zulassen.

Die Entwickler nennen Vega 10 mit zugrundeliegender Grafik-IP GFX 9 als GPU. Das kommt erst einmal als Überraschung, weil AMD bei den Desktop-Grafikkarten mit der Reihe Radeon RX 5700 auf Navi mit RDNA-Architektur alias GFX 10 gewechselt ist.

Vega statt Navi

GPU-seitig wäre ein sogenannter Shrink, das heißt eine Verkleinerung durch einen modernen Fertigungsprozess ohne große Änderungen an der Architektur, gar nicht abwegig. GPU-Leistung für den anvisierten Notebook-Markt hat schon Picasso genug. Erfahrung mit Vega in 7 nm hat AMD bereits mit der Vega-20-GPU auf der Radeon VII gesammelt.

Da die Übertragungsrate des (DDR4-)Speichers bei APUs die 3D-Performance begrenzt, würde eine stärkere Grafikeinheit unter Umständen gar nichts bringen. Der Name Vega 10 spricht für zehn statt elf Compute Units mit 640 statt 704 Shader-Rechenkernen. Die fehlenden Einheiten ließen sich durch höhere Taktfrequenzen ausgleichen – mit einem 7-nm-Prozess wäre das kein Problem.

Spekulationen über eine schnellere APU mit einem HBM2-Speicherchip auf dem Träger kursieren indes mit jeder Generation. Konkrete Anzeichen für eine solche gibt es auch mit Renoir nicht.

Monolithischer Siliziumchip?

Im Desktop und Server wechselte AMD mit Zen 2 auf ein Chiplet-Design, das den I/O-Bereich von den Rechenkernen trennt. Bei den APUs ergäbe eine Aufteilung in mehrere Dies dann Sinn, wenn AMD eine leistungsstärkere, größere GPU verwenden wollte. Das war bisher aber nie das Ziel des Chipherstellers. Stattdessen sollen die Zen-APUs für Marktanteile bei Notebooks sorgen, vor allem in der Mittelklasse.

Bei den Mobilgeräten ist die Größe des Prozessors wichtiger als im Desktop: Je kleiner der Träger ausfällt, desto flexibler sind die Notebook-Hersteller mit ihren Mainboard-Designs. Ein Multi-Chip-Modul würde mehr Platz in Anspruch nehmen. Außerdem fallen AMDs Margen bei den APUs traditionell geringer aus als bei den reinen CPUs – jeder gesparte Quadratmillimeter ist da willkommen, um die Fertigungskosten zu reduzieren.

Ein monolithisches Die würde darüber hinaus den Verdrahtungsaufwand verringern. Bei den Zen-2-CPUs hat AMD den L3-Cache verdoppelt, um Latenzen der Chip-zu-Chip-Kommunikation zu verstecken. In einem einzelnen Siliziumchip ließe sich der Zwischenspeicher verkleinern, wo wir wieder beim Aspekt Chipflächesparen wären.

Nicht zu vergessen ist der Entwicklungsaufwand, um eine GPU als Chiplet in einem Kombiprozessor zu integrieren. Mit Zen 2 und Navi hat AMD dieses Jahr nicht nur zwei neue Architekturen gebracht, sondern diese auch von 14/12 auf 7 nm geschrumpft. Das dürfte bereits reichlich Arbeitsressourcen in Anspruch genommen haben. Für ein drittes Großprojekt wird es da knapp. Auch an dieser Stelle bringt die Wiederverwendung von Vega Vorteile.

Die Frage nach der Anzahl der Rechenkerne

AMD organisiert jeweils vier Rechenkerne in einem sogenannten Core Complexes (CCX). Renoir kann einen oder zwei CCX, also vier oder acht Kerne, nutzen. Auch an dieser Stelle stellt sich die Frage, welche Marktsegmente AMD bedienen möchte.

Uns würde es nicht wundern, wenn AMD bei vier Zen-2-Kernen mit 8 MByte L3-Cache bliebe. Die APU ginge zusammen mit einer Vega-10-GPU auf die 100 mm² Chipfläche zu. Intels Ice-Lake-U-Prozessoren haben ebenfalls nur vier Sunny-Cove-Kerne. Sind es bei AMD am Ende doch acht Kerne, wäre das eine positive Überraschung. (mma)