Bayrischer RISC-V-Sicherheitschip mit seL4-Microkernel

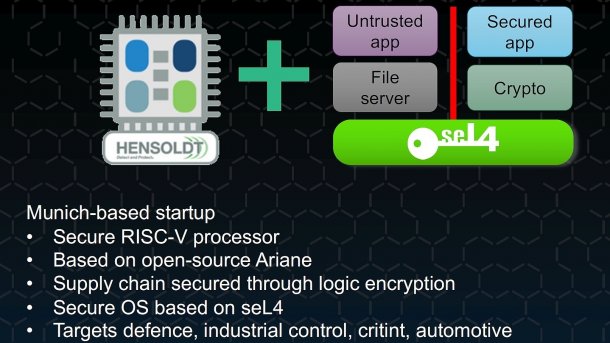

Hensoldt Cyber entwickelt einen Chip für hohe Sicherheitsanforderungen mit RISC-V-Kernen und formal verifiziertem Microkernel.

Konzept Hensoldt Cyber mit RISC-V und seL4

(Bild: CSIRO Data61)

Der Open-Source-Microkernel seL4 ist formal verifiziert und gilt deshalb als besonders sicher. Das Münchner Start-up Hensoldt Cyber entwickelt dazu einen Sicherheitschip mit dem offengelegten RISC-V-Kern Ariane der ETH Zürich, der mit seL4 laufen soll. Er ist für Geräte mit besonders hohen Sicherheitsanforderungen gedacht, darunter Waffensysteme, kritische Infrastrukturen (KRITIS) und Fahrzeuge.

Auf der FOSDEM stellte Professor Gernot Heiser das Projekt vor; er lehrt an der australischen University of New South Wales (UNSW) und arbeitet als Chief Scientist für Software bei Hensoldt Cyber. Die Entwicklung läuft aber auch in der Sparte Data61 der australischen Commonwealth Scientific and Industrial Research Organisation (CSIRO) statt.

Der RISC-V-seL4-Chip soll auch besonderen Schutz gegen Seitenkanalattacken wie beispielsweise Spectre erhalten. Für die Fortentwicklung des Microkernels seL4 wird die seL4 Foundation unter dem Dach der Linux Foundation gegründet. (ciw)