Multi-Chip-Prozessoren: TSMC kombiniert Chips auf 1700 mm² riesigem Interposer

Mit einem neuen Interposer vom weltweit größten Chipauftragfertiger TSMC können Hersteller mehrere Prozessoren mit sechs HBM2-Speicherstapeln kombinieren.

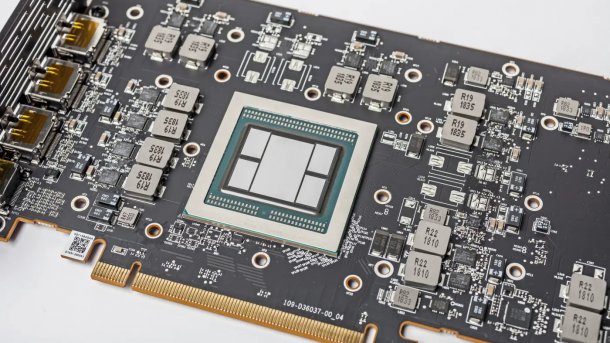

Im Bild: Die Platine von AMDs Radeon VII, deren Vega-20-GPU einen kleineren Interposer nutzt.

(Bild: c't)

Bisherige Silizium-Interposer bilden mit rund 1200 mm² eine Brückenstelle für verschiedene Chips auf einem einzelnen Träger. TSMC erhöht das Flächenlimit auf etwa 1700 mm², womit Hersteller mehr beziehungsweise größere Chips auf einem Träger unterbringen können. Das von TSMC genannte Chip-on-Wafer-on-Substrate (CoWoS) der zweiten Generation ist für Chips vorbereitet, die in den eigenen Prozessen mit Strukturen von 7 und 5 Nanometern vom Band laufen.

Laut TSMCs Mitteilung ist der riesige Interposer primär für Anwendungen in den Bereichen künstliche Intelligenz (KI), Machine Learning und 5G gedacht. Hersteller können beispielsweise mehrere programmierbare Prozessoren (Field Programmable Gate Arrays, FPGAs) mit bis zu sechs HBM2-Speicherstapeln kombinieren. High-Bandwidth Memory (HBM) setzt Silizium-Interposer voraus, weil die 1024 Datenbahnen pro Speicherstapel zu fein für herkömmliche Platinen sind. TSMCs neuer Interposer ist für Übertragungsraten von bis zu 2,7 TByte/s ausgelegt.

Um die Spezifikation des 1700 mm² großen Interposers kümmerte sich Chiphersteller Broadcom, während TSMC die passende Prozesstechnologie ausarbeitete. Mit welchen Strukturbreiten der Interposer hergestellt wird, verrät TSMC nicht.

TSMC umgeht Limit von Belichtungsmaschinen

Die erste CoWoS-Generation stellte TSMC 2016 vor. Mit einer Interposer-Fläche von etwas über 830 mm² bewegte sich der Chip am Limit der Belichtungsgrenze (ca. 850 mm²). Zudem unterstützte er lediglich Übertragungsraten von 1 TByte/s. Größere Interposer wurden bisher mehrfach belichtet (Multi-Patterning), um die Flächenlimitierung zu umgehen.

Beim 1700 mm² großen Interposer setzt TSMC auf "Mask-Stitching", fügt also mehrere Belichtungsmasken zusammen. Im August 2019 zeigte der Chipauftragsfertiger auch einen 2500 mm² großen Interposer mit zwei 600-mm²-Prozessoren und acht HBM2-Stacks, der es bisher aber noch nicht zur Marktreife geschafft hat.

Interposer bei AMD und Nvidia

Für Endkunden setzte bisher lediglich AMD ab Mitte 2015 auf Träger mit mehreren Siliziumchips: Die Fiji-GPU mit vier HBM1-Stacks kam auf der Radeon R9 Fury X zum Einsatz. Zuletzt erschien die Radeon VII mit Vega-20-GPU und vier HBM2-Stacks. Bei den Navi-Grafikkarten der Serie Radeon RX 5000 ist AMD auf GDDR6-Speicher umgeschwenkt, der ähnliche Übertragungsraten über weniger Datenbahnen mit höherer Taktfrequenz erreicht, ohne über einen Interposer direkt an den Grafikchip gekoppelt zu sein.

Nvidia nimmt die Mehrkosten für einen Interposer ausschließlich bei Beschleunigerkarten für Server in Kauf. Auf der Tesla V100 sitzt die Volta-GV100-GPU mit 815 mm² großem Grafikchip und vier HBM2-Stacks. (mma)