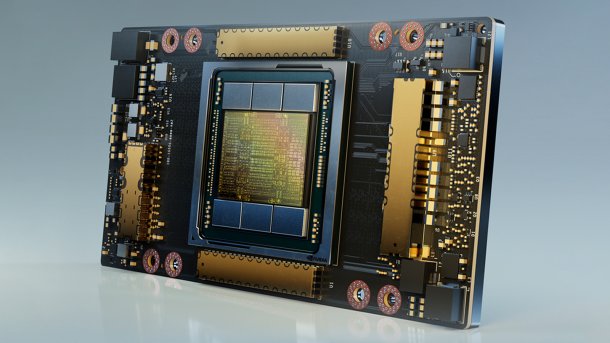

Nvidias A100 mit Ampere-Architektur: Der KI-Beschleuniger im Detail

Ein genauerer Blick auf die Ampere-Architektur zeigt, was an Nvidias Versprechen von 20-facher Leistung im Vergleich zum Vorgänger dran ist.

(Bild: Nvidia)

Der A100 ist Nvidias neuer Beschleuniger für das Rechenzentrum und der erste Chip mit der neuen Ampere-Architektur. Er ist mit spezialisierten, aber flexiblen Tensor-Kernen sowohl für das rechenaufwendigere Training als auch die vergleichsweise einfache Anwendung bereits trainierter neuronaler Netze (Inferencing) geeignet. Dadurch soll er für Betreiber von Rechenzentren schmackhaft werden, die sich beim A100 nicht auf eine einzige Anwendungsmöglichkeit wie bei spezialisierten und hocheffizienten Inferencing-Chips wie etwa Googles TPU v3 festlegen müssen.

Außerdem eignet sich der A100 dank hoher Leistung bei doppeltgenauen Gleitkommaberechnungen auch für klassisches High-Performance-Computing (HPC), wie es Supercomputer häufig durchführen. In veränderter Ausrichtung soll die grundlegende Architektur später auch Basis für die GeForce-Spielergrafikkarten werden. 9,7 Billionen Rechenschritte pro Sekunde (TFlops) bei doppeltgenauen Berechnungen sind schon einmal 25 Prozent mehr als beim V100 – und da kämpft der A100 noch mit stumpfen Waffen: Der Hauptfortschritt bei der Rechenleistung steckt mit Faktor 2 bis 256 in den Tensor-Kernen.

Ampere (sprich: "Em-pier") ist der Name für die Architektur selbst, der A100 das erste Beschleunigerprodukt damit. Es wird bereits ausgeliefert – unter anderem an den Supercomputer-Betreiber Argonne National Labs in den USA, der damit die Covid-19-Forschung beschleunigen will, und an das Forschungszentrum Jülich sowie die Rechenzentren des Karlsruher Instituts für Technologie und der Max-Planck-Gesellschaft bei München.

Das war die Leseprobe unseres heise-Plus-Artikels "Nvidias A100 mit Ampere-Architektur: Der KI-Beschleuniger im Detail". Mit einem heise-Plus-Abo können Sie den ganzen Artikel lesen.